5. Архитектура сигнальных процессоров.

5.1. Введение. Основные задачи обработки сигналов. Методы обработки сигналов.

Терминология сокращений:

ЦОС – цифровая обработка сигналов

DSP – Digital Signal Processing

Сигнальные процессоры – процессоры ЦОС – процессоры DSP.

Четыре основные задачи ЦОС:

- Фильтрация

- Распознавание

- Сжатие

- Генерация (синтез сигналов)

Основные практические приложения ЦОС:

- фильтрация сигналов в условиях пассивных и активных помех;

- кодирование и декодирование информации;

- распознавание видео-, звуковых (речевых), радио- и др. сигналов;

- генерация и обработка изображений;

- спектральный анализ;

- ……

Самое характерное для процессоров ЦОС:

- использование Гарвардской архитектуры (с модификациями!);

- сокращение длительности командного цикла;

- использование конвейеризации (2 – 3 каскада);

- параллельная обработка инструкций;

- аппаратные умножители (и делители!??);

- плавающая точка;

- специальные команды …..

Появление процессоров ЦОС на рынке вслед за появлением персональных компьютеров – начало 80-х годов. Первый(?) процессор DSP – японская корпорация NEC выпустила однокристальную микро-ЭВМ со специальными свойствами MPD7720, но осталась почти незамеченной. В 1982 году фирма Texas Instruments начала выпуск процессора TMS32010. Множество удачных технических решений, сохранение концепции NEC, невысокая цена, востребованность - промышленный стандарт де-факто. Кратко основные характеристики:

- командный цикл 160 – 280 нс;

- ОЗУ на 144 или 256 слов;

- ПЗУ программ до 4К слов;

- ППЗУ с ультрафиолетовым стиранием до 4К слов;

- внешнее ОЗУ до 4К слов без потери производительности;

- разрядность АЛУ и аккумулятора 32 разряда;

- умножитель 16 х 16 бит с 32-битным результатом;

- восемь 16-разрядных внешних портов;

- 16-разрядная внешняя шина с пропускной способность 50 Мбит/с.

Наблюдалось несколько «поколений». Главные производители микросхем кроме NEC и Texas Instruments сегодня Motorola, AT&T Microelectronics, Analog Devices, ATI и др.

Главное направление в методах обработки сигналов связано с максимально эффективными алгоритмами быстрого преобразования Фурье (БПФ), алгоритмами сжатия изображений и сигналов вообще, применением специального кодирования и др.

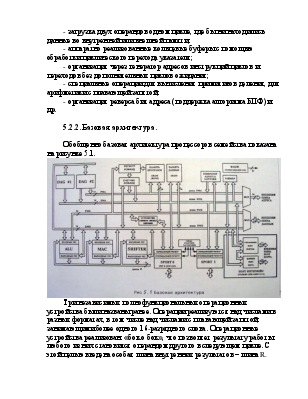

Далее в главе рассмотрено семейство процессорных устройств ADSP21xx, насчитывающее в настоящее время более 15 микросхем различного назначения на единой базовой архитектуре. По сравнению с универсальными процессорами, применяемыми в персональных компьютерах, их производительность для выполнения алгоритмов обработки сигналов выше в 4 – 8 раз.

5.2. Основные характеристики и базовая архитектура семейства ADSP-21xx

Семейство процессоров ADSP21xx представляет из себя набор программируемых однокристальных микропроцессоров с общей базовой архитектурой, оптимизированной для ЦОС и некоторых других приложений, требующих быстрых вычислений. Процессоры семейства существенно отличаются друг от друга внутренними устройствами на кристалле: память на кристалле (наличие, тип и объем), таймер, последовательный порт (порты), порт ПДП, порты интерфейса с хост-процессором, аналоговый интерфейс и др. реализованы в различных моделях микросхем семейства. Кроме того отдельные микросхемы различаются используемыми корпусами, напряжением питания (5В и 3,3В), наличием режима низкого потребления энергии, используемой частотой и длиной командного цикла.

5.2.1. Общие сведения о составе функциональных устройств

Каждый процессор семейства содержит три независимых полнофункциональных операционных устройства: арифметико-логическое устройство (arithmetic/logic unit – ALU), умножитель-накопитель (multiplier/accumulator – MAC) и устройство «барабанного» сдвига (barrel shifter – SHIFTER). Операционные устройства работают с 16-разрядными данными нескольких форматов и обеспечивают аппаратную поддержку вычислений с различной точностью.

Вторая важная функциональная составляющая – генераторы адресов. Процессоры содержат два выделенных генератора адресов данных и генератор адресов инструкций (команд). Генераторы обеспечивают адреса для доступа как к внутренней, так и ко внешней памяти. Генератор адресов инструкций поддерживает условное ветвление в одинарном цикле, т.е. обеспечивает исполнение цикло без замедления на ветвление. Два генератора адресов данных позволяют исполнять двухадресные команды за один цикл.

В семействе процессоров ADSP21xx используется модифицированная Гарвардская архитектура, в которой память данных хранит данные, а память программ хранит как программы, так и данные. Во всех процессорах семейства кроме одного (самого первого – ADSP 2100, ныне не используемого) имеется память на кристалле, которая отображается на часть общего адресного пространства данных и программ. Быстродействие этой памяти позволяет процессору в течение цикла считать 2 операнда из памяти данных и инструкцию из памяти команд (программ).

Последовательные порты (Serial PORT – S-PORT) обеспечивают полный последовательный интерфейс с аппаратурой сжатия/восстановления данных и позволяют вести обмен с большим кругом стандартных последовательных устройств. Каждый S-PORT может работать с синхронизацией от внутреннего таймера или тактироваться извне.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.