- Эмуляторы EZ-ICE. Программное средство обеспечивает поддержку аппаратной отладки систем ADSP-21xx. Обеспечивают внешнюю внутрисхемную эмуляцию с небольшим или нулевым замедлением. Платы EZ-ICE представляют собой дешевые аппаратные платформы для запуска примеров приложений.

5.3. Интерфейс процессоров ADSP-21xx с памятью.

Семейство процессоров ADSP-21xx использует модифицированную Гарвардскую архитектуру, в которой память данных содержит данные, а память программ хранит как инструкции (команды), так и данные. Если процессор (стандартный случай) содержит ОЗУ и/или ПЗУ на кристалле, то часть адресного пространства памяти данных и памяти инструкций находятся на чипе. Эти процессоры также имеют адресное пространство загрузочной памяти вдобавок к адресным пространствам памяти данных и инструкций.

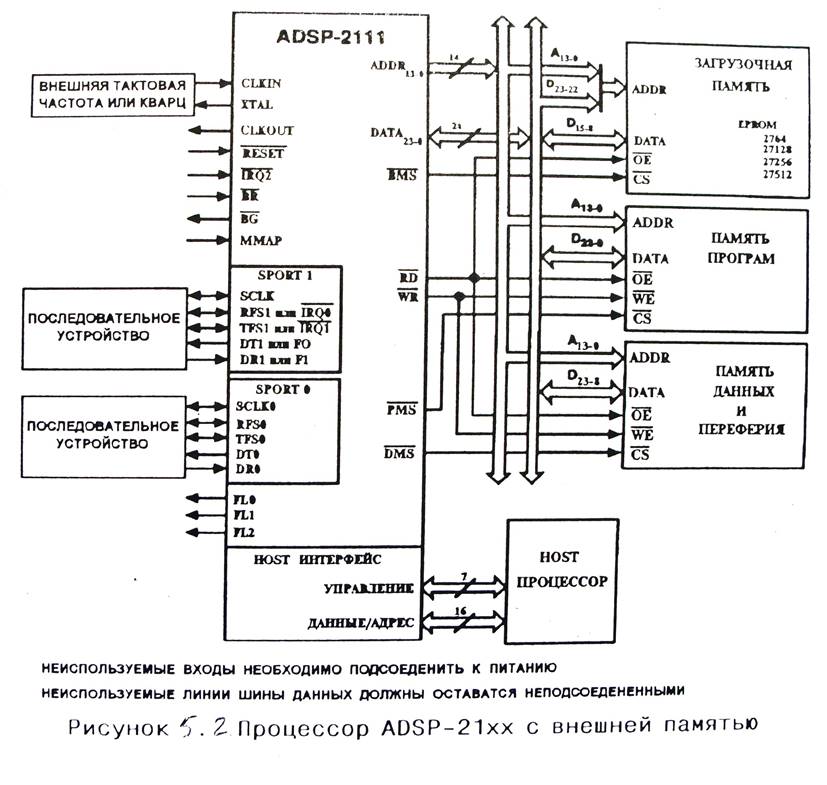

Напомним, что в процессорах, которые имеют внутреннюю память, внутренняя шина адреса памяти инструкций PMA и внутренняя шина адреса памяти данных DMA мультиплексированы в единую шину адреса, выведенную наружу чипа. Также внутренние шина данных памяти инструкций PMD и шина данных памяти данных DMD мультиплексированы в единую шину данных, выведенную наружу чипа. 16 старших разрядов внешней шины данных используются как шина DMD, т.е. D23-8 используются как DMD15-0.

Итак, есть три различных адресных пространства: памяти данных, памяти инструкций и загрузочной памяти. Сигналы PMS, DMS и BMS показывают, какая из них в данный момент используется. Так как шина данных и шина инструкций используют одни и те же физические линии, то если требуется более одной пересылки данных в/из внешней памяти за период выполнения одной инструкции, будет использован дополнительный процессорный цикл на исполнение команды. Общая конфигурация связи процессора с внешней памятью показана на рисунке 5.2.

5.3.1. Интерфейс с загрузочной памятью.

Вся внутренняя память программ или любая её часть могут быть загружены из внешней (загрузочной) памяти с использованием специальной процедуры. Для взаимодействия с недорогими микросхемами EPROM процессор загружает инструкции побайтно.

Автоматическая загрузка после сброса зависит от состояния сигнала управления картой памяти MMAP (Memory Map Control Signal). Начальная загрузка происходит, если сигнал MMAP находится в состоянии логического нуля во время общего сброса процессора. Но начальная загрузка может быть также инициирована программно после сброса.

Процессоры семейства, имеющие порт HIP, могут быть загружены как с использованием интерфейса с загрузочной памятью, так и с использованием хост-компьютера. Состояние линии BMODE определяет используемый метод (0 – загрузка из памяти, 1 – загрузка через порт HIP).

Сигнал BR (активный низкий) распознается во время начальной загрузки. Шина предоставляется после загрузки текущего байта. Некоторые модели процессоров семейства (ADSP-2161, ADSP-2162, ADSP-2164 и др.) содержат ПЗУ инструкций на чипе и поэтому для их устройств начальная загрузка не происходит.

Загрузочные страницы.

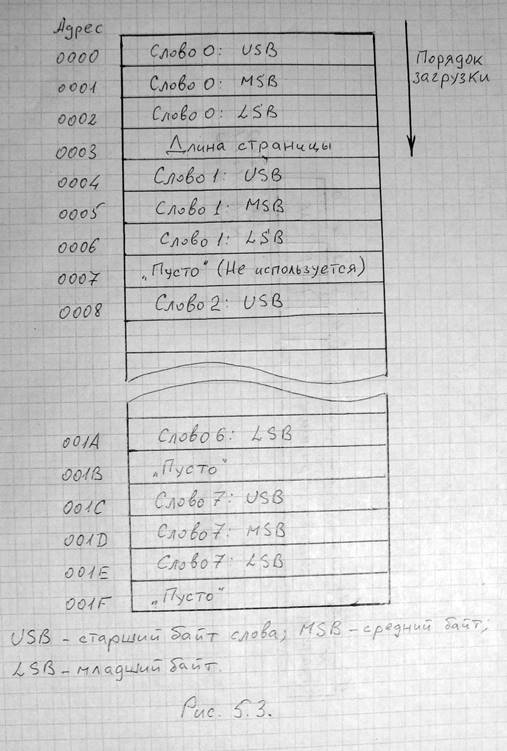

Загрузочная память состоит из 8 страниц, каждая из которых может быть длиной до 8Кбайт. Каждый четвертый байт каждой страницы «пустой» за исключением одного первого, который содержит длину страницы. Каждый набор из трёх байтов между последовательными «пустыми» байтами содержит инструкцию. Сначала читается длина страницы, а затем байты загружаются один за другим, начиная с верха страницы. Это сокращает время загрузки коротких страниц.

Длина страницы

вычисляется так: количество 24-битных слов памяти программ делится на 8 и минус

1. Так, например, длина страницы равная 0 соответствует генерации адресов для 8

слов, расположенных в 32 последовательных байтах (8/8-1=0; 24/8=3 – столько

байт в каждом слове; 3+1=4 – добавление «пустых» байт; 4х8=32). - См. рисунок

5.3.

Начальная загрузка и программный сброс.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.