Переполнение (AV) Перенос (AC) Содержимое AR

0 0 по операции ALU

0 1 по операции ALU

1 0 0111111111111111

1 1 1000000000000000

(Внимание! Забегаем вперёд! Реализация режима «насыщения» существенно отличается от аналогичного режима MAC, где режим устанавливается в самой команде.) Регистр AF не подчиняется режиму «насыщения».

Режим «защёлки» переполнения ALU, устанавливаемый битом 2 регистра MSTAT, приводит к тому, что флаг переполнения AV сохраняет установленное по переполнению значение, несмотря на то, что следующие команды могли не генерировать переполнение. Флаг AV может быть очищен только прямой записью 0 через шину DMD.

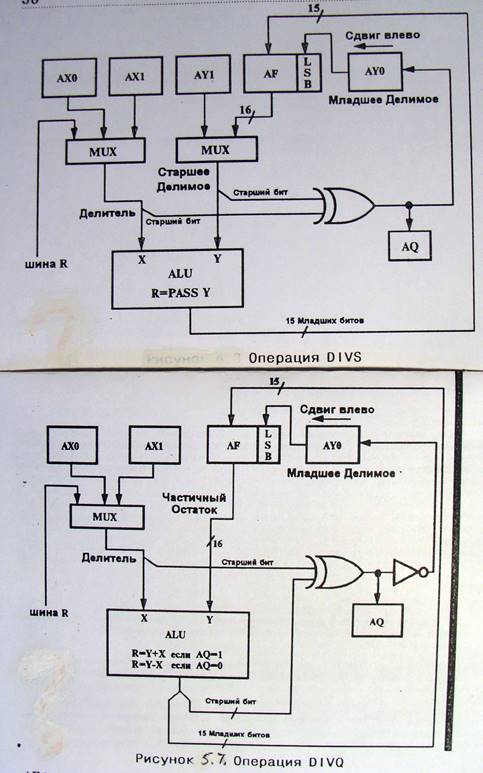

Функция деления (не операция, а по сути дела подпрограмма!) реализуется дополнительной сдвиговой схемой, не показанной на рис.5.6. Деление обеспечивается реализацией двух «примитивов деления», которые поддерживают алгоритм деления без восстановления остатка. Деление может быть знаковым или беззнаковым, но делимое и делитель должны иметь один тип.

Стандартное деление (с одинарной точностью) предполагает 32-битное делимое и 16-битный делитель и выполняется за 16 командных циклов. Также могут быть вычислены частные меньшей и большей разрядности при некоторых коррекциях алгоритма. Делитель может располагаться в AX0, AX1 или в регистре R любого операционного устройства. Старшая часть знакового делимого может располагаться в AY1 или в AF. Старшая часть беззнакового делимого должна располагаться только в AF. Младшая часть делимого должна располагаться только в AY0. По завершении операции частное находится в AY0.

Логические схемы

«примитивов деления» DIVS и DIVQ

показаны на рис.5.7. Первая из них выполняется только

один раз (один цикл) и только в начале деления знаковых чисел. Вторая (DIVQ)

выполняется 15 раз после первой или 16 раз при выполнении знакового или

беззнакового деления соответственно. Поскольку при беззнаковом делении операция

DIVS не используется, то вначале флаг AQ

(признак знака частичного остатка) должен быть принудительно сброшен в 0.

Первая из них выполняется только

один раз (один цикл) и только в начале деления знаковых чисел. Вторая (DIVQ)

выполняется 15 раз после первой или 16 раз при выполнении знакового или

беззнакового деления соответственно. Поскольку при беззнаковом делении операция

DIVS не используется, то вначале флаг AQ

(признак знака частичного остатка) должен быть принудительно сброшен в 0.

Проанализируйте работу приведённых схем в соответствии с алгоритмом деления без восстановления остатка самостоятельно!

Схемы корректно формируют в случае необходимости признак переполнения AV.

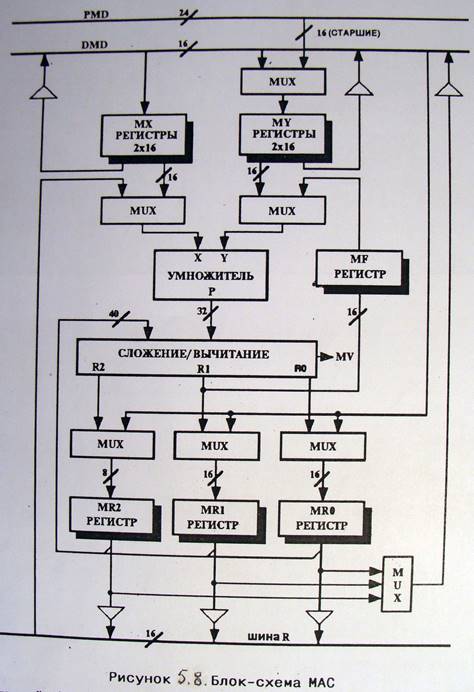

5.4.2. Умножитель/накопитель MAC.

Это операционное устройство обеспечивает высокоскоростное умножение, умножение с накоплением (или вычитанием) результата, «насыщение» и очистку результата.

Структурная схема MAC показана на рис.5.8.

Операционная схема умножителя имеет два входных 16-битных порта X и Y и один 32-битный выходной порт результата P. Результат умножения (32-разрядное произведение) поступает на 40-битный сумматор, который прибавляет или вычитает результат умножителя к регистру результата MR. Ширина регистра результата MR составляет 40 бит; он состоит из трёх регистров: двух 16-битных MR0 и MR1 и 8-битного MR2. Сумматор совместно с регистром MR имеют такую ширину для того, чтобы допустить промежуточные переполнения при выполнении нескольких операций подряд. Флаг переполнения умножителя MV (multiplier overflow) устанавливается, если значащие разряды появились выше 32-битной границы регистра MR.

Входные и выходные регистра устройства MAC, а также режимы записи/чтения в них аналогичны таковым для ALU.

Результат работы сумматора загружается либо в регистр обратной связи MF, либо в регистр результата MR. Регистр обратной связи MF позволяет использовать биты 16 – 31 результата непосредственно как операнд Y в следующем цикле. 40-битный регистр результата MR обеспечивает прямую загрузку любого из трёх регистров MR0, MR1 и MR2 через шину DMD или запись их содержимого через шину DMD или шину промежуточных результатов R.

MAC, аналогично ALU, содержит

второй (теневой) банк регистров, что «тенью» показано на рис.5.8.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.