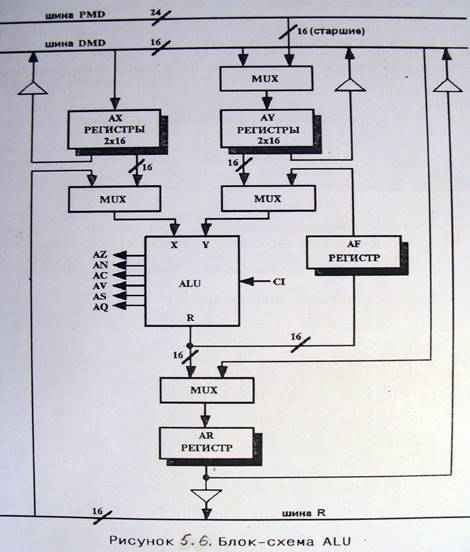

Структурная схема ALU показана на рис.5.6.

ALU имеет три группы 16-битных регистров, доступных для программиста: X, Y – регистры операндов и R – регистр результата. ALU использует входной сигнал переноса (CI), который соответствует биту переноса в регистре признаков результата («арифметического состояния» - ASTAT). ALU генерирует шесть признаков результата («статусных сигналов»):

- AZ – нулевой результат;

- AN – отрицательный результат;

- AC – перенос;

- AV – переполнение разрядной сетки;

- AS – знак результата;

- AQ – состояние частного.

Установка признаков происходит в конце командного цикла в регистре ASTAT.

Входной порт X операционной схемы может принимать данные из двух источников: из регистров AX или шины результата (R). Шина результатов соединяет выходные регистры всех операционных устройств, позволяя им быть непосредственными источниками операндов инструкций. Блок регистров AX состоит из 2-х регистров: AX0 и AX1. Эти регистры читаемы и могут быть записаны через шину DMD. Выход блока регистров AX таков, что один из них может обеспечивать подачу операнда для схемы ALU, в то время как другой может использоваться для записи в память через шину DMD.

Входной порт Y операционной схемы может принимать данные из двух источников: из набора регистров AY или из регистра обратной связи AF. Блок регистров AY состоит из 2-х регистров: AY0 и AY1. Эти регистры читаемы и могут быть записаны через шину DMD. Выход блока регистров AY таков, что один из них может обеспечивать подачу операнда для схемы ALU, в то время как другой может использоваться для записи в память через шину DMD.

Результат работы операционной схемы ALU поступает либо в регистр обратной связи AF – внутренний регистр ALU, который затем можно использовать результат непосредственно как операнд Y, либо в регистр результата AR. Регистр результата AR может записываться через шину DMD или через шину результатов R. Он также непосредственно загружаем через шину DMD.

Набор команд позволяет осуществлять чтение регистров ALU через шину PMD, но при этом нужно использовать устройство обмена между шинами DMD/PMD.

Все регистры, связанные с ALU могут, как читаться, так и записываться в одном цикле. Регистры читаются в начале цикла и записываются в конце. Новое значение, записанное в регистр, не может быть считано до начала следующего цикла.

Внимание! ALU содержит два полных набора операционных регистров AX0, AX1, AY0, AY1, AR и AF, что показано на рис.5.6. как «тень». В каждый момент времени работы процессора доступен лишь один набор. Другой набор регистров может быть сделан активным для очень быстрого переключения контекстов, например при обработке прерывания. Это означает, что новая задача, такая как обработка прерывания, может быть выполнена без запоминания текущего состояния регистров. Выбор «первичного» или «вторичного» набора регистров определяется младшим битом в регистре состояния (режима работы и статуса) процессора MSTAT. Если в этом бите 0, то используется «первичный» набор регистров, а если 1, то «вторичный».

Список функций ALU:

R = X + Y;

R = X + Y + CI - сложение с переносом;

R = X – Y

R = X – Y – CI – 1 - вычитание с заёмом;

R = Y – X;

R = Y – X – CI – 1;

R = – X;

R = – Y;

R = Y + 1;

R = Y – 1;

R = X;

R = Y;

R = 0 - обнуление (очистка) результата;

R = ABS (X) - результат равен абсолютному значению X;

R = X AND Y - поразрядное логическое И;

R = X OR Y - поразрядное логическое ИЛИ;

R = X XOR Y - поразрядное логическое «исключающее ИЛИ» (сумма по модулю 2);

R = NOT X - поразрядная инверсия X;

R = NOT Y - поразрядная инверсия Y.

Список инструкций стандартизован с подавляющим большинством простых микропрограммируемых процессоров и RISC-процессоров.

Особые режимы.

Регистр AR имеет режим работы, при котором он после операции автоматически устанавливается в максимальное положительное или максимальное отрицательное значение (режим «насыщения»). Этот режим задается установкой бита 3 регистра MSTAT. При включении режима значение, получаемое в AR, зависит от комбинации значений флагов AC и AV, сгенерированных ALU в текущем цикле:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.