- организация через генератор адресов инструкций циклов и переходов без дополнительных циклов ожидания;

- специальные операции для вычисления примитивов деления, для арифметики с плавающей запятой;

- организация реверса бит адреса (поддержка алгоритма БПФ) и др.

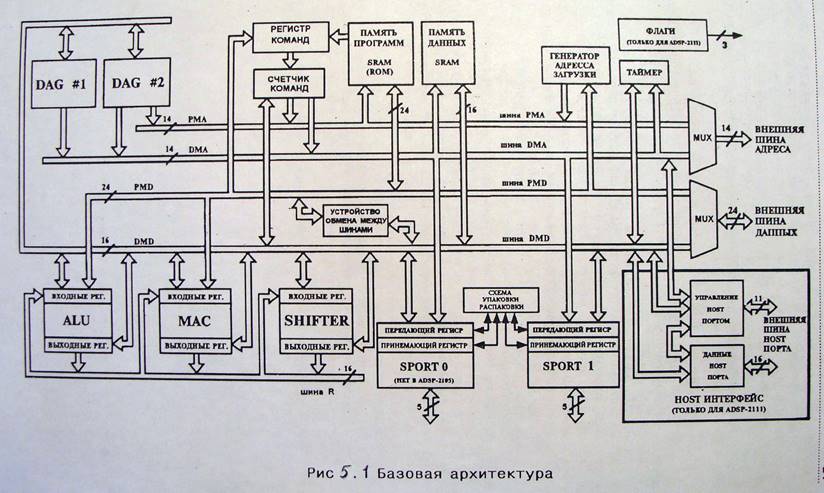

5.2.2. Базовая архитектура.

Обобщенно базовая архитектура процессоров семейства показана на рисунке 5.1.

Три независимых полнофункциональных операционных устройства были названы ранее. Операции реализуются над числами в разных форматах, в том числе над числами с плавающей запятой, занимающими более одного 16-разрядного слова. Операционные устройства реализован «бок о бок», что позволяет результату работы любого из них становится операндом другого в следующем цикле. С этой целью введена особая шина внутренних результатов – шина R.

Все три операционных устройства содержат входные и выходные регистры, которые доступны через внутреннюю шину данных памяти данных (DMD). Регистры обеспечивают буферизацию между операционными устройствами и памятью.

Два выделенных генератора адресов данных DAG1 и DAG2 обеспечивают формирование адресов памяти данных, когда данные пересылаются из выходных или во входные регистры операционных устройств. Каждый генератор запоминает до 4-х адресных указателей. Когда указатель используется для косвенной адресации, он может автоматически модифицироваться значением в заданном регистре после исполнения инструкции. Два генератора обеспечивают генерацию двух адресов данных в одном цикле, т.е. поддерживать двухадресные инструкции. С каждым указателем может быть ассоциирована длина для автоматической реализации кольцевых буферов. (Эта возможность также используется последовательными портами и аналоговым интерфейсом для автоматической передачи данных.)

Различия:

DAG1 может генерировать адреса только для памяти данных, но в его выходном адресе может меняться порядок следования битов перед выдачей на шину, что облегчает адресацию в алгоритмах radix-2 БПФ;

DAG2 может генерировать адреса, как для памяти данных, так и для памяти программ.

Функции счетчика команд выполняет генератор адресов команд, который не только инкрементацией, а многообразно формирует адреса инструкций для памяти программ. Он управляет регистром инструкций, который содержит исполняемую в данный момент команду. Регистр инструкций буферирует исполнение программы. Команды загружаются в регистр в течение одного цикла, а исполняются в течение следующего, одновременно с загрузкой следующей команды. Чтобы минимизировать циклы ожидания устройство выполняет условные переходы, вызовы и возвраты из подпрограмм за один цикл. Счетчик/генератор имеет внутренний счетчик вложенности циклов и стек циклов для работы без потерь времени.

Внутренние устройства процессоров связаны пятью шинами:

- шина адреса памяти данных DMA (Data Memory Address); шина имеет ширину 14 бит, что обеспечивает доступ к 16 Кб данных;

- шина адреса памяти инструкций PMA (Program Memory Address); шина имеет ширину 14 бит, что обеспечивает доступ к 16 Кб инструкций и данных;

- шина данных памяти данных DMD (Data Memory Data); шина имеет ширину 16 бит, что обеспечивает пересылку содержимого любого регистра процессора в любой другой регистр или в/из памяти в течение одного цикла; адрес памяти данных формируется из абсолютного значения, записанного в инструкции (абсолютная адресация), или из генератора адресов данных (косвенная адресация); только косвенная адресация возможна для адресации данных в памяти программ;

- шина данных памяти инструкций PMD (Program Memory Data); ширина этой шины – 24 бита, что обеспечивает загрузку 24-разрядной команды;

- шина внутренних результатов – шина R.

Первые четыре шины мультиплексированы наружу микросхемы в две шины – шину адреса и шину данных; адресное пространство выбирается сигналами BMS, DMS и PMS (все – активный низкий).

Шина PMD также может быть использована для пересылок данных в/из операционных устройств напрямую или через устройство обмена между шинами PMD и DMD. Устройство обмена позволяет пересылать данные с одной шины на другую и содержит логику сопряжения для преодоления разницы ширины в 8 бит.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.