Если процессор работает только с памятью на чипе, то он может загружать в операционные устройства 2 операнда и загружать следующую инструкцию в одном цикле. Также возможно загружать один из этих трех операндов из внешней памяти без потери производительности.

5.3.3. Интерфейс с памятью данных.

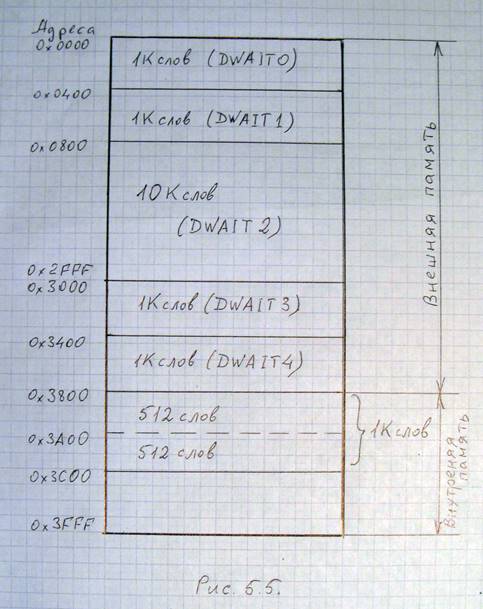

Процессоры семейства адресуют 16К 16-битных слов памяти данных (512 или 1024 слова на чипе). Память данных на чипе всегда начинается с адреса 0х3800; регистры управления процессором отображаются на старшие адреса адресного пространства: 0х3C00 – 0х3FFF. Первые по номерам адресов 14К слов адресного пространства доступны для хранения дополнительных данных вне процессора.

Данные передаются по старшим 16 битам 24-битной шины PMD, которая выведена наружу. Сигнал DMS –выбора памяти данных (активный низкий) указывает на то, что на шину адреса поступил адрес памяти данных.

Две управляющие линии устанавливают направление передачи данных: RD - чтение данных (активный низкий) и сигнал WR – запись данных (активный низкий).

Доступ к внешней памяти данных аналогичен доступу к внешней памяти инструкций.

Адресное

пространство памяти данных представлено на рис.5.5.

Каждая из пяти областей (разной длины) внешней памяти имеет своё программируемое количество циклов ожидания DWAITi (i = 0 – 4). Это сделано для того, чтобы использовать зоны адресного пространства не только с разными чипами памяти, но и для работы с периферийными устройствами разной производительности. Регистры периферийных устройств и любых схем памяти отображаются на общее адресное пространство. Регистр управления тактами ожидания имеет пять отдельных 3-битных полей DWAITi (кодируется от 0 до 7 циклов) для соответствующих зон памяти.

При использовании сигналов запроса шины BR и предоставления шины BG процессор может отдавать управление внешними шинами, предоставляя доступ внешним устройствам, например хост-процессору.

Если включен особый GO-режим, то процессор продолжит исполнять инструкции с использованием исключительно внутренней памяти. Если же GO-режим выключен, то процессор всегда останавливается перед предоставлением шины. Последовательные порты и HIP-порт остаются активными во время предоставления шины, безразлично останавливался ли процессор или нет. На период предоставления внешней шины (по запросу BR – активный низкий и установке BG – активный низкий) сигналы WR, RD, PMS, DMS и BMS устанавливаются в третье состояние. Если процессору и приходится останавливаться, то его внутреннее состояние не меняется предоставлением шины. После удовлетворения и снятия запроса нормальная работа процессора продолжается с того места, где она была прервана.

5.4. Архитектура операционных устройств.

Все операционные устройства в процессорах семейства 16-битные устройства с фиксированной точкой. Почти все операции подразумевают представление знаковых чисел в форме «дополнения до двух». Остальные же используют беззнаковые числа или просто строки битов. Специальная поддержка имеется для организации многословных вычислений и блочной плавающей арифметики. Некоторые нюансы работы с форматами будут пояснены в разделах описания архитектур операционных устройств.

Формат «дополнения до двух» это обычный дополнительный код в формате дроби 1.15. В нём левый бит числа обозначает его знак, а 15 оставшихся бит представляют числа от -1 до почти +1 (почти из-за несимметричности представления знаковых чисел).

Иллюстрация:

Принятое Формат 1.15 Десятичное шестнадцатиричное значение обозначение

0х0001 0.000000000000001 0.000031

0х7FFF 0.111111111111111 0.999969

0хFFFF 1.111111111111111 -0.000031

0х8000 1.000000000000000 -1.000000

5.4.1. Арифметико-логическое устройство.

По набору операций ALU в процессорах семейства абсолютно стандартно. Единственным дополнением следует считать включение в состав устройства специальной логической схемы для организации многоциклового деления.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.