После программного или аппаратного сброса, если MMAP=0 происходит начальная загрузка. Начальная загрузка после аппаратного сброса всегда загружает загрузочную страницу с номером 0. После программного сброса загрузка может быть произведена программно из любой из восьми различных страниц. Поле выбора загрузочной страницы (BPAGE) находится по адресу памяти 0х3FFF в системном регистре и определяет из какой страницы должна происходить загрузка.

Для загрузки из некоторой страницы загрузочной памяти необходимо установить поле BPAGE на нужную страницу и затем, по этому же адресу памяти, установить бит инициирования загрузки (BFORCE). После этой установки начинается программно инициированная начальная загрузка.

Кроме схемы выбора страницы и, возможно, числа циклов ожидания обращения к загрузочной памяти различий между программно инициированной начальной загрузкой и «аппаратной» загрузкой по сбросу нет. Количество циклов ожидания для доступа к загрузочной памяти находится по адресу 0х3FFF в системном регистре. Это поле может быть установлено в значение 0 до 7 (соответствует числу циклов ожидания при доступе). Значение после начального аппаратного сброса – 3 цикла ожидания (по умолчанию).

Последовательность начальной загрузки.

Для выполнения

операции загрузки генератор адресов загрузочной памяти генерирует адреса соответствующих

байтов и загружает внутреннюю память. Внутренняя память программ загружается

начиная со старших адресов. Например, если в процессор загружаются восемь

24-битных слов, то первое слово записывается по адресу памяти инструкций 0007,

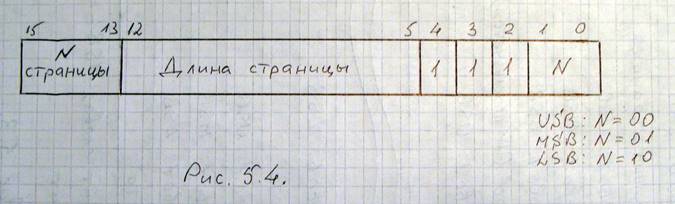

а последнее – по адресу 0000. Структура загрузочного адреса приведена на

рисунке 5.4.

Последнее 24-битное слово (последняя команда памяти программ) загружается в процессор первым. Порядок загрузки байтов: USB, затем LSB, затем MSB. После этого слово-указатель декрементируется и адресует предыдущее слово памяти программ и т.д. Например для загрузки из страницы с номером 0 с самой короткой длиной (восемь 24-битных слов – длина страницы равна 0 – см. рис.5.3.) будут сгенерированы следующие адреса в следующей последовательности:

1) 0003 – считывание длины страницы;

2) 001C – старший байт USB последнего слова;

3) 001E - младший LSB байт последнего слова;

4) 001D – средний байт последнего слова;

5) 0018, 001A, 0019;

6) 0014, 0016, 0015 …

Процесс продолжится до загрузки слова с адресом 0.

5.3.2. Интерфейс с памятью программ.

Процессоры семейства адресуют 16К 24-битных слов памяти программ (до 2К на чипе). Процессор выдает 14-битный адрес на 14-битную шину адреса памяти инструкций PMA, которая выведена наружу чипов для доступа к внешней памяти. Инструкции или данные из памяти программ передаются по 24-битной шине данных памяти инструкций PMD, которая выведена наружу. Для исполнения инструкций, которые требуют одновременно доступа к внешней памяти инструкций и к внешней памяти данных, данные из памяти инструкций читаются первыми, а затем данные из памяти данных. Сигнал PMS (выбора памяти данных) указывает на то, что на шину адреса поступил адрес памяти инструкций.

Две управляющие линии устанавливают направление передачи данных. Сигнал RD - чтение данных (активный низкий) указывает на процесс чтения из памяти; сигнал WR – запись данных (активный низкий) указывает на процесс записи в память.

Доступ к памяти на чипе не затрагивает внешних шин. Сигналы PMS, DMS, RD и WD остаются высокими, а шины адреса и данных находятся в третьем состоянии.

Внешняя память инструкций имеет программируемое поле циклов ожидания памяти инструкций PWAIT в регистре управления. После включения там по умолчанию находится значение соответствующее 7 циклам ожидания.

В зависимости от состояния входа MMAP адресное пространство памяти инструкций отображается по-разному:

- при MMAP=0 во время загрузки первые 2К занимает внутренняя память, а потом идут внешние 14К памяти;

- при MMAP=1 – наоборот.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.