Логічні ключі, що використовують збіднені MESFETи.

Розглянуті вище логічні елементи характеризуються тим, що використовують як збагачені, так і збіднені транзистори, що суттєво ускладнює технологічні процеси їх виготовлення. Також необхідно при виробництві дуже чітко забезпечувати порогові рівні, щоб коливання напруги і перешкоди не змогли привести до хибних спрацювань. Одним з альтернативних рішень, яке ліквідує вказані проблеми, є побудова логічних елементів з використанням лише збіднених транзисторів.

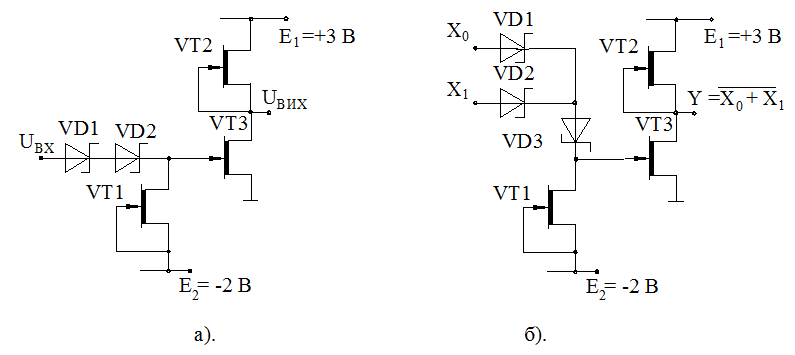

На рис.2.53 приведена схема базового логічного елемента, в якому використовуються лише збіднені MESFETи. Сімейство логічних елементів такого типу має назву FL (FET logic). Основу логічного елемента складає переключаючий транзистор VT2, навантаженням якого є такий же транзистор VT1, включений в режимі перетворювача напруга – струм. Оскільки порогова напруга збіднених транзисторів негативна, то до входу транзистора VT2 необхідно прикладати негативну напругу для його вимикання. З другої сторони вихіний низький рівень напруги на витоці ключа буде завжди позитивним. Звідси витікає, що логічні рівні витоку транзистоа VT2 несумісні з рівнями,

Рис.2.53. необхідними для входу ключа. Проблема несумісності

розв’язується просто шляхом здвигу напруги на витоці транзистора на величину,

рівну падінню напруги на двох діодах Шоткі VD1 і VD2, що приблизно рівна 1.4 В.

Для забезпечення постійного рівня зміщення необхідно, щоб через них протікав

струм незмінної величини, що забезпечується транзистором VT3. Для забезпечення

гарантованих умов роботи транзистора VT3, нижній його електрод- витік,

приєднаний до негативної напруги Е2, величина якої вибрана дещо

більшою, ніж найнижчий рівень

Рис.2.53. необхідними для входу ключа. Проблема несумісності

розв’язується просто шляхом здвигу напруги на витоці транзистора на величину,

рівну падінню напруги на двох діодах Шоткі VD1 і VD2, що приблизно рівна 1.4 В.

Для забезпечення постійного рівня зміщення необхідно, щоб через них протікав

струм незмінної величини, що забезпечується транзистором VT3. Для забезпечення

гарантованих умов роботи транзистора VT3, нижній його електрод- витік,

приєднаний до негативної напруги Е2, величина якої вибрана дещо

більшою, ніж найнижчий рівень

Рис.2.54.

вихідної напруги ключа. Транзистор VT3 одночасно генерує струм, необхідний для перезаряду паразитних конденсаторів при низькому рівні вихідної напруги, “підтягуючи”, тим самим низький рівень до нуля.

Транзистор VT4, приведений на рис.2.53, зображений як вхід слідуючої мікросхеми.

FL -інвертори мають набагато вищі рівні перешкодостійкості, ніж схеми DCFL. В той же час вони вимагають двох джерел живлення. FL – інвертори легко можуть бути використані для побудови логічних елементів АБО-НІ шляхом приєднання паралельно VT2 аналогічних транзисторів.

Логічні елементи на основі діодів Шоткі (SDFL)

Якщо діоди, що використовуються для забезпечення здвигу рівня вихідної напруги перенемсти на вхід логічного елемента, то отримаємо схему, що приведена на рис.2.54,а. Модифікована схема працює майже повністю так, як її попередній аналог. Отримання логічного елемента. Що реалізує функцію АБО-НІ забезпечується простим приєднанням допоміжного діода Шоткі, паралельно діоду VD1(рис.2.54,б ).

Така схемотехніка відома як Schottky diode FET logic (SDFL). SDFL на відміну від інших MESFET технологій займає меншу площу на кристалі, оскільки логічні функції забезпечуються за допомогою допоміжного діода а не транзистора, який більш технологічно складний і займає більшу площу на кристалі.

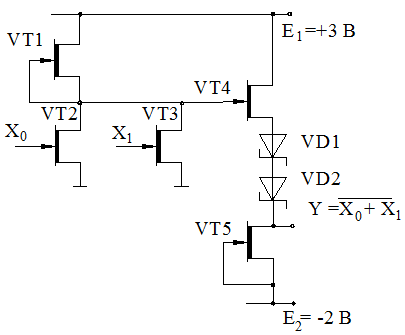

Буферизована FET логіка

Буферизована FET логіка

Іншою модифікацією базового FL інвертора є схема, що зображена на рис. В цій схемі зміщення рівня забезпечується на виході логічного елемента. Така схемотехнічна особливість побудови виходу логічного елемента забезпечує мільш високу навантажувальну здібність по вихідному струму, забезпечуючи одночасно зменшення часової затримки при перемиканні з низького вихідного рівня до високого.

Реальна величина затримки

Рис.2.55. розглянутих арсенід- галієвих структур не перевищує 100 пСек.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.