Базовим елементом, який використовується для побудови різноманітної схемотехніки є n – канальний польовий транзистор з скороченою назвою MESFET (metal semiconductor field effect transistor). Технологічно такий транзистор, на відміну від кремнієвих будується не на домішкових структурах, а на підкладці з чистого GaAs, який має дуже низьку провідність і є напівізолюючою структурою. Така особливість суттєво спрощує технологічні задачі ізоляції різних приладів одної мікросхеми і, тим самим, дає можливість суттєво зменшити паразитні ємності як між окремими транзисторами, так і між транзисторами і заземленням.

Канал в структурі транзистора будується на основі n – домішкових структур. Тільки на них будуються MESFET. Поряд з транзистором технологічно легко виготовляються діоди Шоткі, які широко використовуються в схемотехніці надвисокочастотних приладів. Р- MESFET не мають таких переваг, як n- домішковіі прилади. Цей недолік приводить до ускладнення схемотехніки базових логічних елементів.

Реальні величини затримок інверторів на базі MESFET транзисторів складають від 10 до 100 пікосекунд, що є головною перевагою технології. Недоліками є порівняно висока споживаєма потужність, вузький діапазон робочих напруг, вища, ніж інших технологій, вартість. Напруга живлення логічних елементів знаходиться в межах 1.2 – 1.5 В.

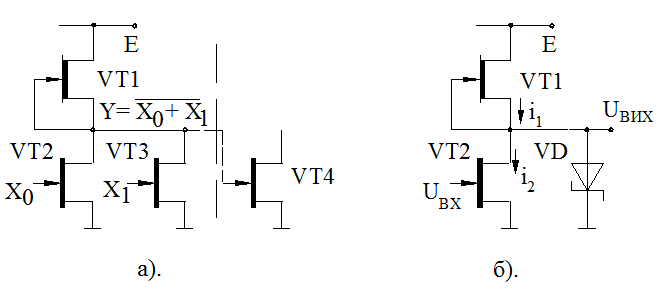

Рис.2.52.

Одна з перших серій, які почали виготовлятись на базі арсенід галієвих напвпровідників є DCFL ( direct coupled FET logic). Схема базового елемента її приведена на рис.2.52,а. Схема використовує збіднений транзистор VT1 і збагачені транзистори VT2, VT3, використовуємі для прийому вхідних сигналів. Логічний елемент реалізує логічну операцію 2АБО-НІ.

Розглянемо особливості роботи схеми. Коли вхідна напруга, представлена логічним сигналом Х0, прикладається до затвору транзистора VT2 і має величину меншу, ніж її порогове значення UП, транзистор VT2 буде знаходитись в виключеному стані. Величина порогової напруги для MESFET є позитивною з типовим рівнем 0.1-0.3 В. Якщо вихід базового елемента вільний, (не приєднаний до входів іншимх мікросхем), то напруга на виході буде близькою до Е, оскільки кола для протікання струму від транзистора VT1 немає. Транзистор VT1 працює в режимі джерела струму і при відсутності кола для протікання струму переходить в режим насичення. Реально схема працює на аналогічний логічний елемент (транзистор VT4 слідуючої мікросхеми). В такому випадку, струм, що генерується транзистором VT1, проходить через транзистор навантаження. Вище було відмічено, що поряд з арсенід- галієвим транзистором монтується діод Шоткі. В розглядаємій структурі базового логічного елемента він приєднується паралельно входу MESFET. При прямому протіканні струму через діод на ньому має місце падіння напруги біля 0.7 В. В цьому заключається суттєва різниця між розглядаємими схемами і КМОН структурами. На рис.2.52,б приведена схема DCFL інвертора з навантаженням в вигляді діода Шоткі. При величині вхідної напруги, меншій порогового рівня, струм через ключ VT2 і2 = 0 і весь струм і1 від транзистора VT1 протікає через прямозміщений діод Шоткі, забезпечуючи падіння напруги 0.7 В. Оскільки напруга живлення низька (1.2 – 1.5 В) , то транзистор VT1 буде працювати в активному режимі. Як тільки вхідна напруга перевище порогове значення транзистора VT2, останній включиться і почне пропускати струм і2. Спочатку величина цього струму буде малою, але вона буде зменшувати струм, що протікав через діод Шоткі. Напруга на VD також буде зменшуватись. Як тільки забезпечиться рівність і1 = і2 , діод Шоткі перестане проводити струм і закриється, а подальше зростання вхідної напруги приведе до зниження падіння напруги на транзисторі VT2, яка має значення 0.1 – 0.2 В. Звідси маємо, що діапазон вихідних напруг такого ключа знаходиться в інтервалі 0.1 – 0.7 В, що суттєво сприяє зниженню потужності на перемикання і інтервалу затримки.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.