Приведений аналіз показує, що мікросхему можна використовувати для побудови дешифратора шестирозрядного двійкового коду на 64 виходи лише шляхом їх пірамідальної побудови. Для цього 8 дешифраторів запаралелюються по входах А0-А2, а вхід А3 підключається до виходів керуючого дешифратора через інвертори. Входи А0-А2 керуючого дешифратора є старшими розрядами адресної шини х0-х5.

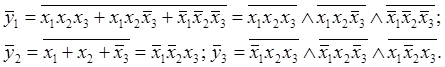

69. Для вирішення цієї задачі перетворимо функцію до вигляду

Із приведених функцій бачимо:

1.

функція

1.

функція ![]() може бути отримана за допомогою звичайного

інвертора підключеного до виходу, відповідного

може бути отримана за допомогою звичайного

інвертора підключеного до виходу, відповідного ![]() = 1002

= 410

= 1002

= 410

2. функція ![]() отримується об’єднанням через

елемент И виходів, відповідних х3х2х1

= 1112 = 710;

отримується об’єднанням через

елемент И виходів, відповідних х3х2х1

= 1112 = 710; ![]() = 0112

= 310;

= 0112

= 310; ![]() = 0002

= 010. Для реалізації функції

= 0002

= 010. Для реалізації функції ![]() необхідно інвертувати у1.

Отже у1 отримується за допомогою трьохвходового елемента І-НЕ

(3І-НЕ).

необхідно інвертувати у1.

Отже у1 отримується за допомогою трьохвходового елемента І-НЕ

(3І-НЕ).

3. Аналогічно функція у3

отримуеться шляхом обєднання виходів ![]() = 1102 = 610;

= 1102 = 610; ![]() = = 0102 = 210;

= = 0102 = 210; ![]() = 510 за допомогою елемента 3І-НЕ. Використаємо мікросхему К155ЛЕ4 3(3І-НЕ).

= 510 за допомогою елемента 3І-НЕ. Використаємо мікросхему К155ЛЕ4 3(3І-НЕ).

Принципова схема, яка реалізує вказані функції приведена на рис. 30.

71. Звернути увагу на рішення задачі №69.

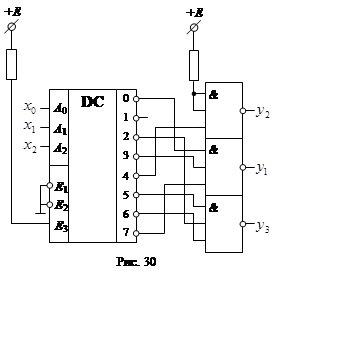

72. Умовне зображення мікросхеми приведено на рисунку 31. Кожен із мультиплексорів має 4 входи і 1 вихід. З’єднані вони лише двома загальними шинами. Для кожного із мультиплексорів є свій вхід дозволень V (1V, 2V).

Для організації мультиплексора 8:1 необхідно мати три адресні шини, що може бути забезпечено додатковими елементами ДД2 і ДД3.

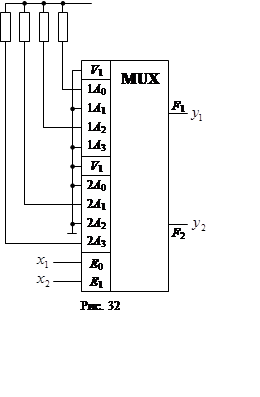

75. Логічна функція, яка описує роботу однієї

секції мультиплексора КІ55КП2 виглядає наступним чином: ![]() .

.

Порівнюючи цю логічну функцію з функцією

Порівнюючи цю логічну функцію з функцією![]() бачимо, що якщо на адресні входи Е0

і Е1 подати логічні змінні х0 і х1

відповідно, на інформаційні входи А0 і А1

подати сигнали, відповідаючі логічній одиниці, а А1, V, А3

– заземлити, то мультиплексор буде реалізовувати задану функцію. Схема, яка

реалізує вказані функції, приведена на рис. 32.

бачимо, що якщо на адресні входи Е0

і Е1 подати логічні змінні х0 і х1

відповідно, на інформаційні входи А0 і А1

подати сигнали, відповідаючі логічній одиниці, а А1, V, А3

– заземлити, то мультиплексор буде реалізовувати задану функцію. Схема, яка

реалізує вказані функції, приведена на рис. 32.

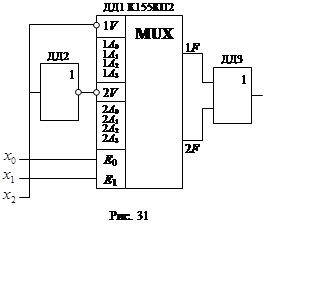

76. Приведемо функцію до досконалої дизюнктивної

нормальної форми: ![]()

Порівнюючи функцію у з логічною функцією, яка

виконується мультиплексором

по прямому входу

Порівнюючи функцію у з логічною функцією, яка

виконується мультиплексором

по прямому входу

![]()

находимо, що інформаційні входи А5, А3, А2, А6 необхідно підключити до джерела живлення, а останні підключити до загальної шини. До адресних входів Е0, Е1, Е2 підключити логічні змінні х1, х2, х3.

77. В розглядаємому випадку є п’ять логічних змінних, тому прямим методом можливо її реалізувати лише на мультиплексорі виду 32:1, а для мультиплексорів 4:1 число адресних входів п = 2.

Тому рішення задачі знаходиться за наступною послідовністю.

Визначаються ранги (кількість повторів) логічних змінних: х1 = х3 =3; х2 = х5 = 2; х4 = 4.

Виділяємо дві змінні (в відповідності з кількістю адрес мультиплексорів) з найбільшими рангами: х3 = 3. х4 = 4.

Перетворимо логічну функцію, вводячи в кожну конюнкцію вибрані логічні змінні:

![]()

Виконуємо

факторизацію функції, виносячи за дужки коньюнкції змінних х3

і х4:

Виконуємо

факторизацію функції, виносячи за дужки коньюнкції змінних х3

і х4:

![]()

Введемо додаткові позначення:

![]()

![]()

![]()

![]()

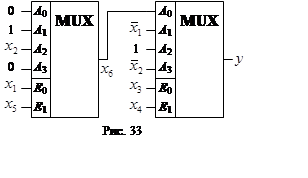

Відмітимо, що функція реалізується за допомогою мультиплексора 4:1. Тому

для реалізації логічної функції у необхідно мати два незалежні мультиплексори

4:1 (рис 33).

Відмітимо, що функція реалізується за допомогою мультиплексора 4:1. Тому

для реалізації логічної функції у необхідно мати два незалежні мультиплексори

4:1 (рис 33).

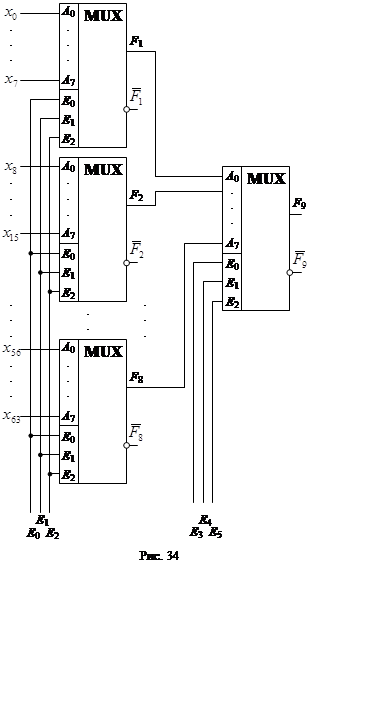

78. Для рішення поставленої задачі можна взяти мультиплексор ТТЛ КІ55КП7 й використовувати його прямий вхід. Для побудови мультиплексора 64:1 неопхідно використати пірамидальний принцип їх включення. Три молодші розряди Е0, Е1, Е2 мультиплексорів повинні вирішувати задачі комутації кожної вісімки входів на вихід відповідного мультиплексора.

Три старші розряди Е3, Е4, Е5 (рис. 34) використовуються для комутації виходів F1…F6 мультиплексорів ДД1-ДД8 на вихід F9 мультиплексора ДД9 [7].

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.