79. Вказівка. Для реалізації мультиплексора 8:1 можна використати мікросхеми К155КП2. Для реалізації мультиплексора можна використати мікросхеми К531ИД14 – подвійний дешифратор демультиплексор; К155ИД4 – демультиплексор 1:4.

Забезпечити роздільне управління комутацією входів мультиплексорів і комутацією входів демультиплексорів.

80. Вказівка. Необхідно звернути увагу на приклад 77.

81. Вказівка. Врахувати, що в мікросхемах КМОП ИС в комутаторах використовуються двонаправлені ключі, які мають однаково низький опір в обох напрямках.

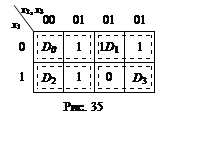

85. Зображуємо функцію на карті Карно (рис. 35). Довільно вибираємо керуючі змінні х1, х2. Це дозволяє восьмиячійкову карту Карно розбити на чотирі двохячійкові карти однієї змінної відповідно при різних комбінаціях значень х1, х2. При цьому кожна двовходова карта буде відповідати одному інформаційному входу D0-D3 (рис. 35).

Із карти Карно отиримуємо: D0 = х3,

D1 = 1, D2 = 0, D3 = х3.

Звідси маємо схему включення мультиплексора.

Із карти Карно отиримуємо: D0 = х3,

D1 = 1, D2 = 0, D3 = х3.

Звідси маємо схему включення мультиплексора.

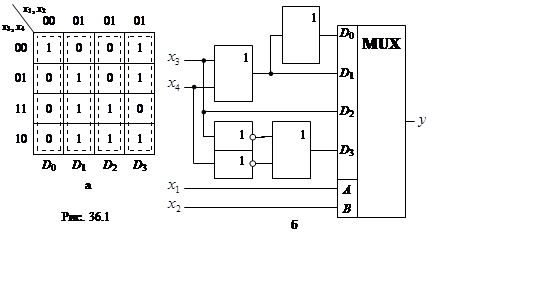

86.  Оскільки використовується мультиплексор з чотирма

входами, то при передачі двох змінних по керуючим входам, на інформаційні

входи подаються остаточні функції двох змінних. Функцію представимо в формі

карти Карно (рис. 36.1а).

Оскільки використовується мультиплексор з чотирма

входами, то при передачі двох змінних по керуючим входам, на інформаційні

входи подаються остаточні функції двох змінних. Функцію представимо в формі

карти Карно (рис. 36.1а).

Виберемо в якості керуючих змінних х1,

х2. В результаті отримаємо чотири функції двох змінних.

Виконуючи мінімізацію кожної функції окремо, матимемо: D0=![]() , D1=

, D1=![]() , D2=

, D2=![]() , D4=

, D4=![]()

Із отриманих результатів, використовуючи додаткові логічні

елементи можемо реалізувати функцію, яка нас цікавить. (рис. 36.1б).

Із отриманих результатів, використовуючи додаткові логічні

елементи можемо реалізувати функцію, яка нас цікавить. (рис. 36.1б).

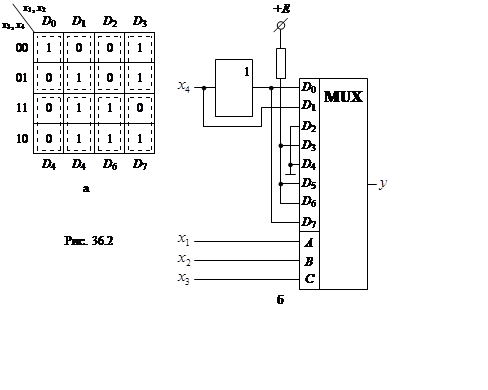

Більш просто розглядаєма функція може бути реалізована

при використанні восьмивходового мультиплексора. Для цього необхідно на

керуючі входи подати три логічні змінні, наприклад х1, х2,

х3. В такому випадку карта Карно буде розбита на 8

двовходових карт (рис. 36.2а). Із отриманих карт маємо проміжні функції D0

=![]() , D1 = х4,

D2 = 0, D3 = 1, D4 = 0, D5

= 1, D6 = 1, D7= =

, D1 = х4,

D2 = 0, D3 = 1, D4 = 0, D5

= 1, D6 = 1, D7= =![]() ,

які дозволяють розробити принципову схему (рис. 36.2б).

,

які дозволяють розробити принципову схему (рис. 36.2б).

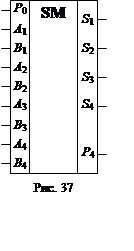

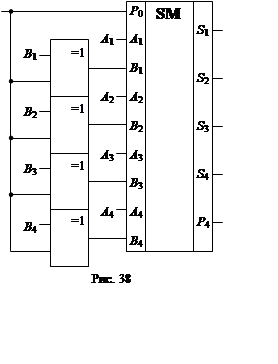

89.  Вказівка. При сумуванні двох чотирьохрозрядних слів необхідно

вхід переносу Р0 заземлити (рис. 37). Для сумування двох

однорозрядних необхідно заземлити входи А3, В3.

В дворозрядному суматорі входами є А1, А2 й

В1, В2, а виходами S1, S2, S3. Останній є виходом переносу. В однорозрядному

суаторі використовуються входи А4,

В4, а виходами є

S4 й Р0 . При сумуванні двох однобайтових слов необхідно наростити два

однотипних суматори. При цьому вихід Р4 суматора напівбайтів

молодших розрядів зєднується з входом Р0 суматора напівбайтів

старших розрядів сумуємих слів.

Вказівка. При сумуванні двох чотирьохрозрядних слів необхідно

вхід переносу Р0 заземлити (рис. 37). Для сумування двох

однорозрядних необхідно заземлити входи А3, В3.

В дворозрядному суматорі входами є А1, А2 й

В1, В2, а виходами S1, S2, S3. Останній є виходом переносу. В однорозрядному

суаторі використовуються входи А4,

В4, а виходами є

S4 й Р0 . При сумуванні двох однобайтових слов необхідно наростити два

однотипних суматори. При цьому вихід Р4 суматора напівбайтів

молодших розрядів зєднується з входом Р0 суматора напівбайтів

старших розрядів сумуємих слів.

90. Для того, щоб виконати віднімання двох чисел в

двійковій системі числення необхідно із двійкового коду віднімаємого отримати

додатковий код, перед цим інвертувавши його. Отже, віднімаєме перед сумуванням  необхідно інвертувати, а для використання додаткового

коду до нього по входу Р0 додаеється одиниця. Якщо

віднімаємим є слово В, то необхідні для віднімання операції можуть

характеризуватися функцією

необхідно інвертувати, а для використання додаткового

коду до нього по входу Р0 додаеється одиниця. Якщо

віднімаємим є слово В, то необхідні для віднімання операції можуть

характеризуватися функцією ![]() .

.

При виконанні операції додавання на вхід Р0

подається низький сигнал, а на входи В – прямий код, тобто ![]() .

.

Порівнюючи отримані формули неважко помітити, що

сигналом, який керує видом операції, є сигнал, який подається на вхід переносу.

Функція ![]() реалізується мікросхемою ВИКЛЮЧАЮЧЕ АБО.

реалізується мікросхемою ВИКЛЮЧАЮЧЕ АБО.

З викладеного легко реалізувати схему для виконання операцій додавання та віднімання (рис. 38).

91. Вказівка 1. Використати шифратор десятичного коду в чьотирьохрозрядний двійковий код.

Вказівка 2. Для отримання доповнення до 9 необхідно зробити віднімач десяткового числа N із числа 9.

92. Код з надлишком 3 отримується додаванням до двійкового коду кода числа 3.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.