В результате выполнения пункта задания и проведения эксперимента над VHDL-моделью были имитированы реальные задержки цифрового узла ИЕ10, что подтверждают результаты верификации.

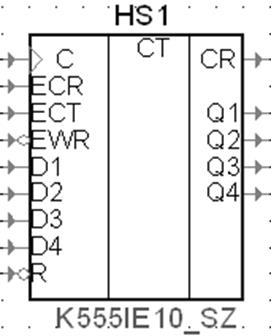

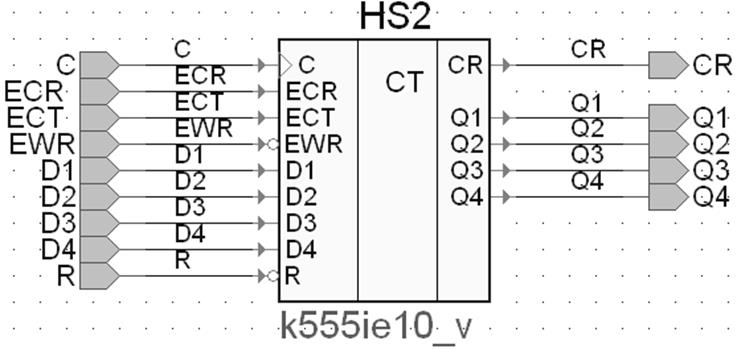

Ниже приведено УГО иерархического символа, поддерживаемого схемой замещения (Рис. 23.).

Рис. 23. Условное графическое изображение узла в виде иерархического символа.

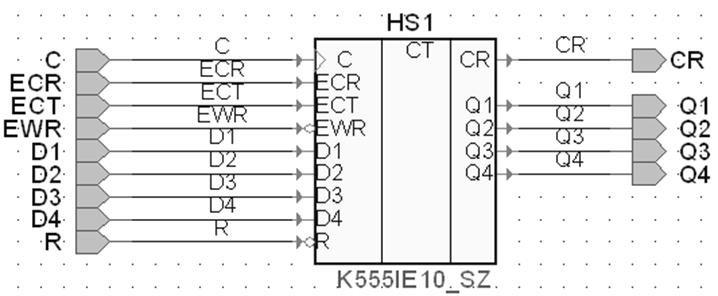

Принципиальная схема замещения узла приведена на стр. 19.(Рис. 24)

Рис. 24. Принципиальная схема замещения иерархического символа (HS1).

Рис. 25. Схема верификации иерархического символа.

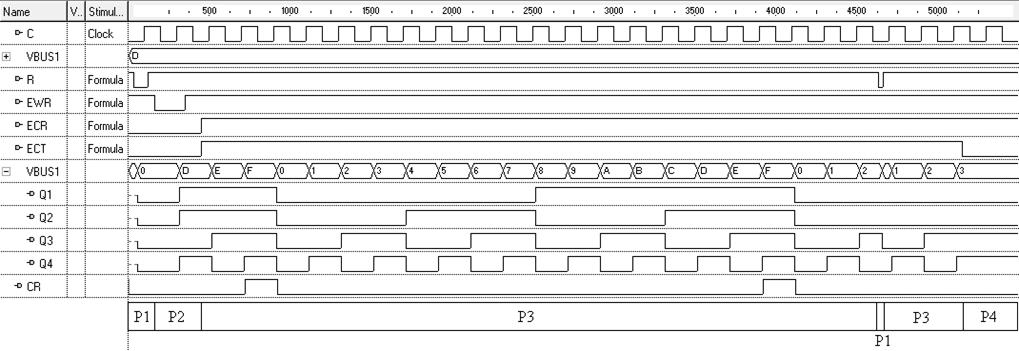

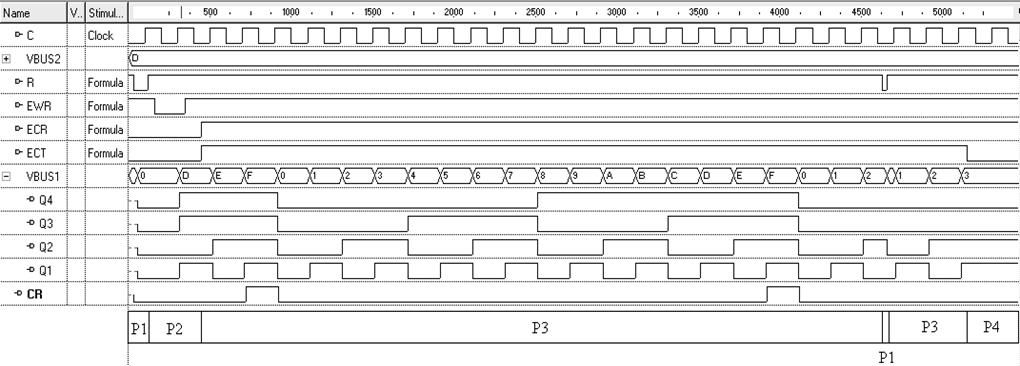

Рис. 26. Результаты моделирования узла.

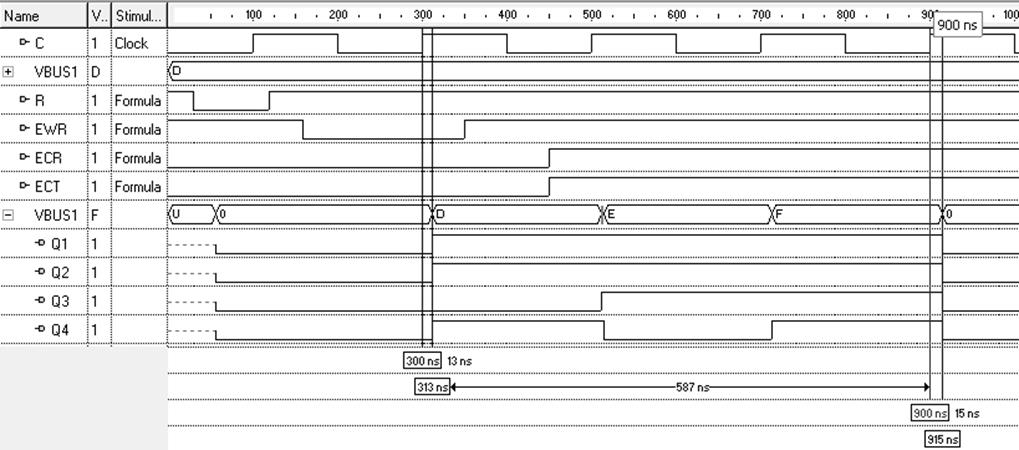

Режимы работы узла (Рис. 26):

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р2 (режим 2) – параллельная загрузка с информационных входов D1-D4 ([Q4,Q3,Q2,Q1]=D).

Р3 (режим 3) – счётный

режим, т.к. все три сигнала ECR, ECT и ![]() имеют высокий уровень.

имеют высокий уровень.

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р3 (режим 3) – счетный режим.

Р4 (режим 4) – хранение, сигнал ECT(вход разрешения счёта) переключается из 1 в 0.

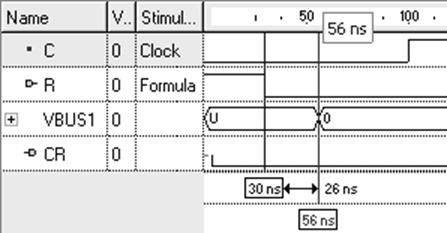

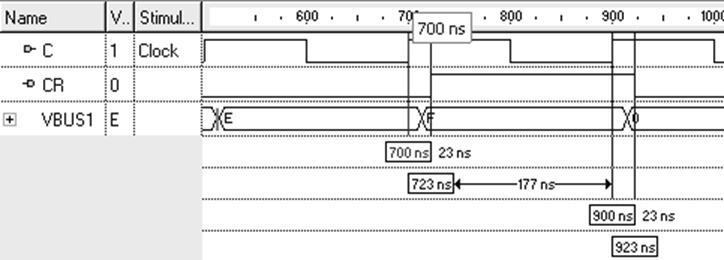

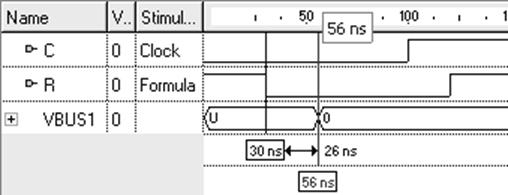

Перейдем к контролю временных соотношений в схеме (Рис. 27,28,29).

Рис. 27. Задержка распространения сигнала вход cброса

![]() – выход данных Q4,Q3,Q2,Q1 - 26нс.

– выход данных Q4,Q3,Q2,Q1 - 26нс.

Рис. 28. Время задержки распространения сигнала при включении/выключении:

вход тактирования C – выход переноса CR - 23нс.

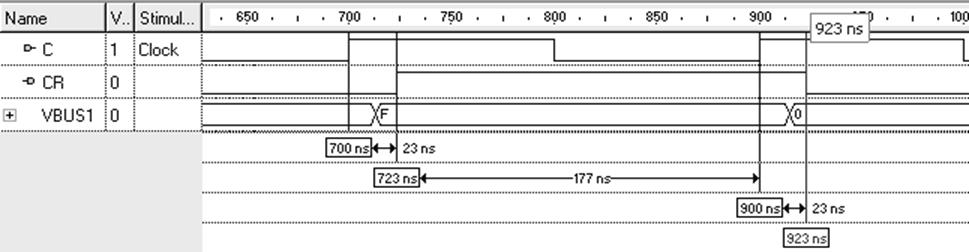

Рис. 29. Время задержки распространения сигнала при включении/выключении

Вход тактирования C – выход данных Q4,Q3,Q2,Q1 (включение 13нс, выключение 15нс).

Исходя из результатов эксперимента, можно прийти к выводу, что узел работает корректно. Все задержки, показанные на временных диаграммах совпадают с табличными, что является подтверждением правильности их имитации.

Поведенческая модель узла приведена на стр. 15.

Рис. 30. Схема верификации узла с подключенной VHDL-моделью (HS2).

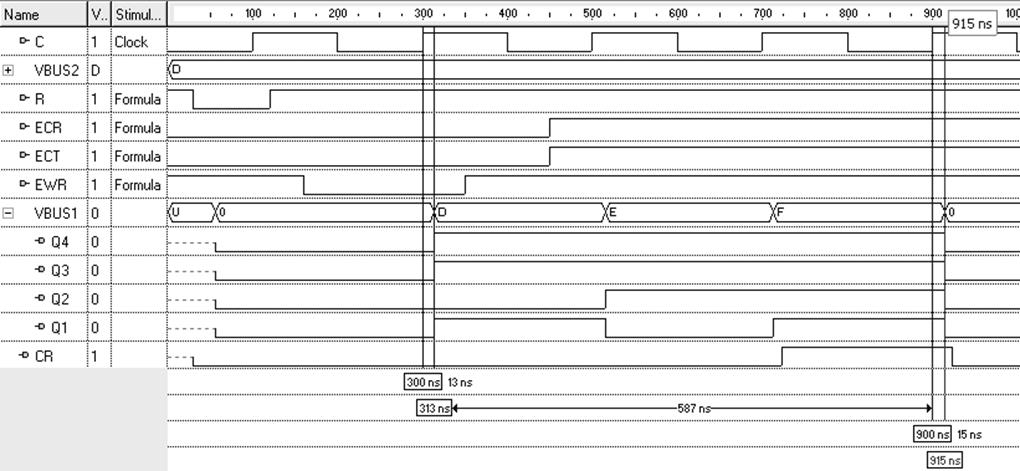

Рис. 31. Временные диаграммы моделирования VHDL-модели узла (HS2).

Режимы работы узла (Рис. 31):

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р2 (режим 2) – параллельная загрузка с информационных входов D1-D4 ([Q4,Q3,Q2,Q1]=D).

Р3 (режим 3) – счётный режим, т.к. все три сигнала ECR, ECT и ![]() имеют высокий уровень.

имеют высокий уровень.

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р3 (режим 3) – счетный режим.

Р4 (режим 4) – хранение, сигнал ECT(вход разрешения счёта) переключается из 1 в 0.

Исходя из результатов эксперимента, VHDL-модель работает корректно. Перейдем к контролю временных соотношений в VHDL-модели (Рис. 32,33,34).

Рис. 32. Задержка распространения сигнала вход cброса

![]() – выход данных Q4,Q3,Q2,Q1 - 26нс.

– выход данных Q4,Q3,Q2,Q1 - 26нс.

Рис. 33. Время задержки распространения сигнала при включении/выключении:

вход тактирования C – выход переноса CR - 23нс.

Рис. 34. Время задержки распространения сигнала при включении/выключении

Вход тактирования C – выход данных Q4,Q3,Q2,Q1 (включение 13нс, выключение 15нс).

Исходя из результатов эксперимента, можно прийти к выводу, что VHDL-модель работает корректно. Все задержки, показанные на временных диаграммах совпадают с табличными, что является подтверждением правильности их имитации.

В ходе выполнения данной курсовой работы было выполнено индивидуальное задание по разработке цифрового узла ИЕ10, созданию его поведенческой модели на языке VHDL в пакетах OrCAD 9.1 и Active-HDL 8.1. Были проведены имитационные эксперименты с разработанным узлом, целью которых являлось подтверждение работоспособности узла и соответствие его временных задержек требуемым. Помимо этого, были «зацементированы» навыки и знания в области применения САПР, проектирования цифровых устройств, программирования на языке описания цифровой аппаратуры VHDL, анализа результатов работы.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.