Q4, Q3, Q2, Q1, CR: OUT std_logic);

END K555IE10_V;

ARCHITECTURE model OF K555IE10_V IS

signal Q_TEMP: STD_LOGIC_VECTOR (3 downto 0);--внутренний шинный сигнал

BEGIN

PROCESS (R, C, EWR, ECR, ECT) -- начало процесса

BEGIN

IF (R='0') THEN--асинхронный сброс

Q_TEMP <= "0000" after 26ns;

CR<= '0';

ELSIF rising_edge(C) THEN--если фронт синхросигнала

IF (EWR ='0') THEN--и EWR=0 то режим параллельной загрузки

IF Q_TEMP(0)='1' THEN Q_TEMP <=(D4,D3,D2,D1) after 15ns;

ELSIF Q_TEMP(0)='0' THEN Q_TEMP <=(D4,D3,D2,D1) after 13ns;

END IF;

-- если EWR,ECR,ECT имеют высокий уровень, счетный режим

ELSIF (ECR='1' AND ECT='1') THEN

IF Q_TEMP(0)='1' THEN Q_TEMP <= Q_TEMP + 1 after 15ns;

ELSIF Q_TEMP(0)='0' THEN Q_TEMP <= Q_TEMP + 1 after 13ns;

IF Q_TEMP(1)='1' THEN Q_TEMP <= Q_TEMP + 1 after 15ns;

ELSIF Q_TEMP(1)='0' THEN Q_TEMP <= Q_TEMP + 1 after 13ns;

IF Q_TEMP(2)='1' THEN Q_TEMP <= Q_TEMP + 1 after 15ns;

ELSIF Q_TEMP(2)='0' THEN Q_TEMP <= Q_TEMP + 1 after 13ns;

IF Q_TEMP(3)='1' THEN Q_TEMP <= Q_TEMP + 1 after 15ns;

ELSIF Q_TEMP(3)='0' THEN Q_TEMP <= Q_TEMP + 1 after 13ns;

END IF;

END IF;

END IF;

END IF;

IF (Q_TEMP ="1110") THEN--генерация флага переноса

CR <='1' after 23ns;

ELSE

CR <='0' after 23ns;

END IF;

END IF;

END IF;

END PROCESS;

-- присвоение выходным сигналам значений внутреннего шинного сигнала

Q1 <= Q_TEMP(0);

Q2 <= Q_TEMP(1);

Q3 <= Q_TEMP(2);

Q4 <= Q_TEMP(3);

END model;

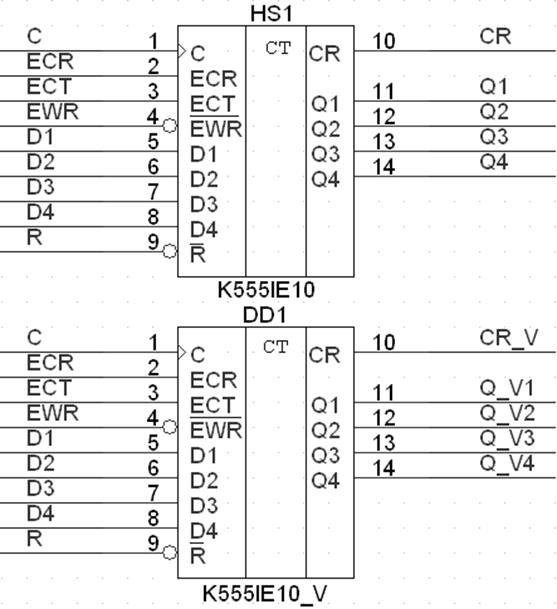

Рис. 18. Схема верификации узла с подключенной VHDL-моделью (DD1) и элемента со схемой замещения (HS1).

7.10. Результаты

моделирования VHDL-модели узла.

7.10. Результаты

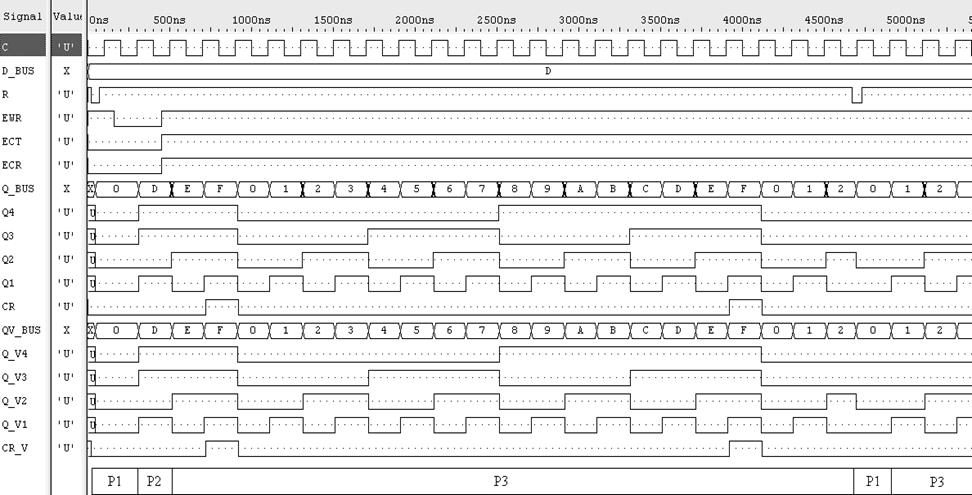

моделирования VHDL-модели узла.Рис. 19. Временные диаграммы моделирования VHDL-модели узла (DD1) и элемента со схемой замещения (HS1).

Режимы работы узла (Рис. 19):

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р2 (режим 2) – параллельная загрузка с информационных входов D1-D4 ([Q4,Q3,Q2,Q1]=D).

Р3 (режим 3) – счётный режим, т.к. все три сигнала ECR, ECT и ![]() имеют высокий уровень.

имеют высокий уровень.

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р3 (режим 3) – счетный режим.

Р4 (режим 4) – хранение, сигнал ECT(вход разрешения счёта) переключается из 1 в 0.

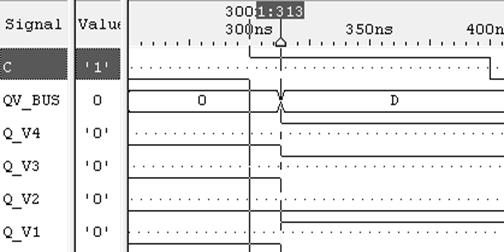

Исходя из результатов эксперимента, VHDL-модель работает корректно. Перейдем к контролю временных соотношений в VHDL-модели (Рис. 20,21,22).

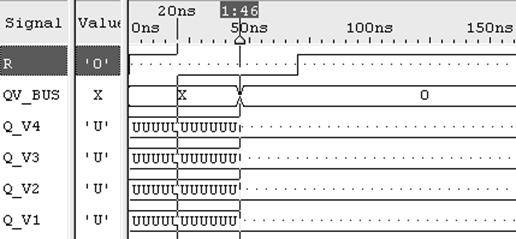

Рис. 20. Задержка распространения сигнала вход cброса

Рис. 20. Задержка распространения сигнала вход cброса

![]() – выход данных Q4,Q3,Q2,Q1 - 26нс.

– выход данных Q4,Q3,Q2,Q1 - 26нс.

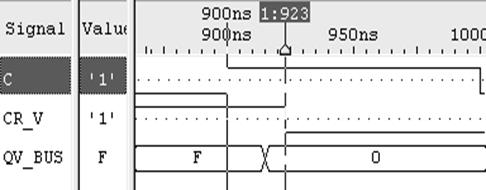

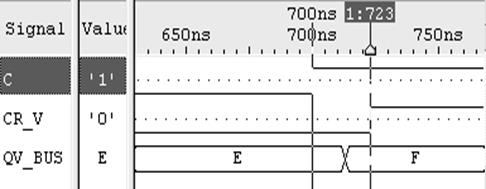

Рис. 21. Время задержки распространения сигнала при включении/выключении:

вход тактирования C – выход

переноса CR - 23нс.

вход тактирования C – выход

переноса CR - 23нс.

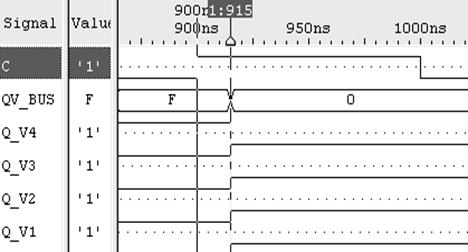

Рис. 22. Время задержки распространения сигнала при включении/выключении

Вход тактирования C – выход данных Q_V4,Q_V3,Q_V2,Q_V1 (включение 13нс, выключение 15нс).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.