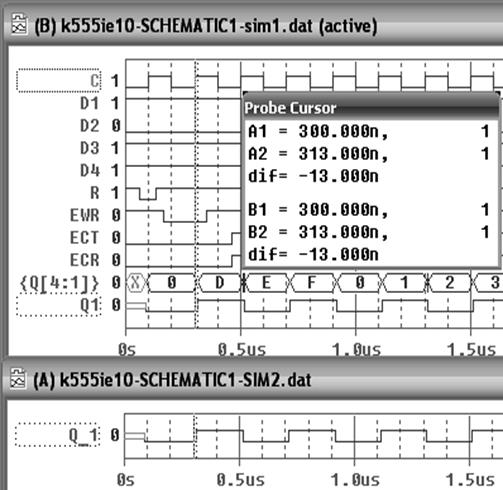

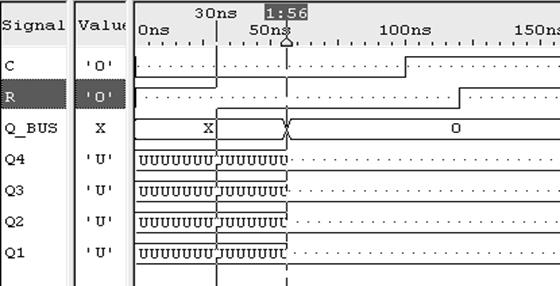

Рис. 6. Задержка распространения сигнала вход cброса

![]() – выход данных Q4,Q3,Q2,Q1 - 26нс.

– выход данных Q4,Q3,Q2,Q1 - 26нс.

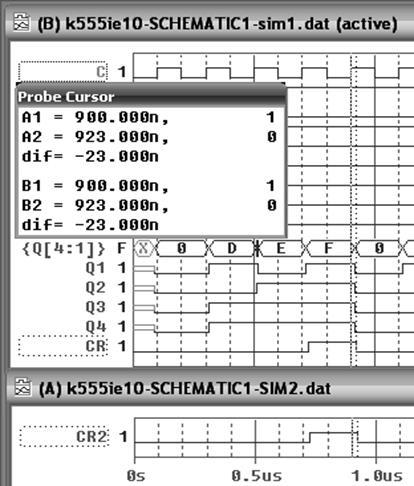

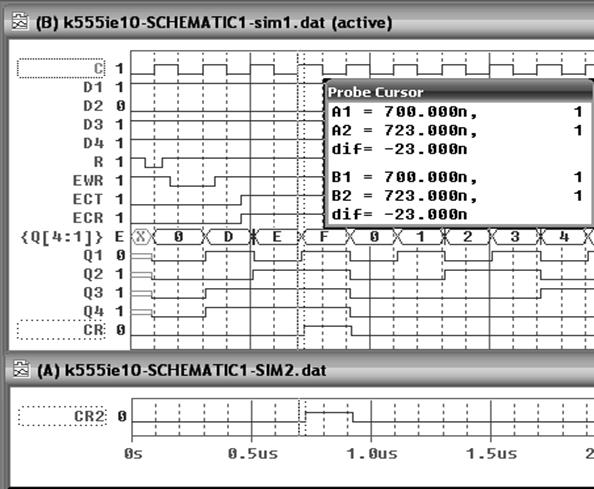

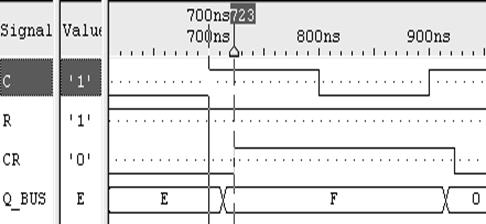

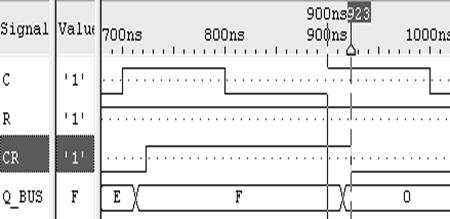

Рис. 7. Время задержки распространения сигнала при включении/выключении:

вход тактирования C – выход переноса CR - 23нс.

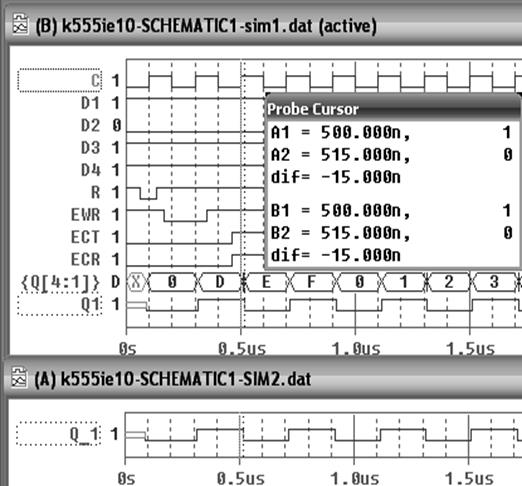

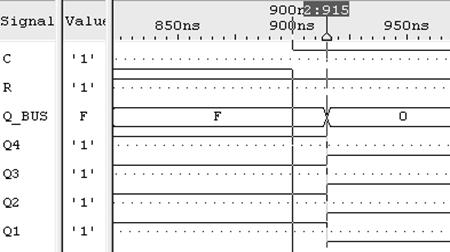

Рис. 8. Время задержки распространения сигнала при включении/выключении

Вход тактирования C – выход данных Q4,Q3,Q2,Q1 (включение 13нс, выключение 15нс).

Все задержки, отображенные на временных диаграммах, совпадают с табличными, что является подтверждением правильности их имитации.

Рис. 9. Работа проектируемого узла при тактовой частоте 25МГц.

Рис. 10. Работа проектируемого узла при тактовой частоте 26МГц.

Таким образом, после оценки предельных скоростных (частотных) возможностей работы счётчика ИЕ10 делаем вывод о его работоспособности при заданных условиях. При частоте повторения тактирующих импульсов 25МГц счётчик работает без сбоев. При увеличении частоты до 26МГц начинаются многочисленные сбои и ошибки, расхождения в работе при сравнении с зарубежным аналогом, предложенным библиотекой 74ls (Рис. 10.).

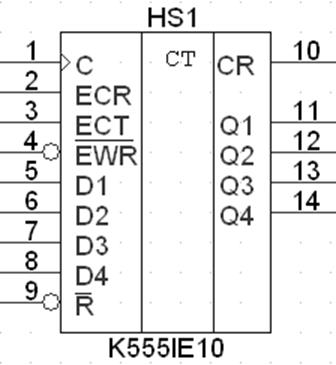

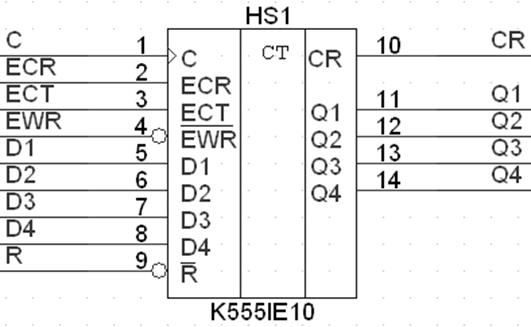

Условное графическое обозначение проектируемого символа (Рис. 11.):

Рис. 11. Условное графическое обозначение.

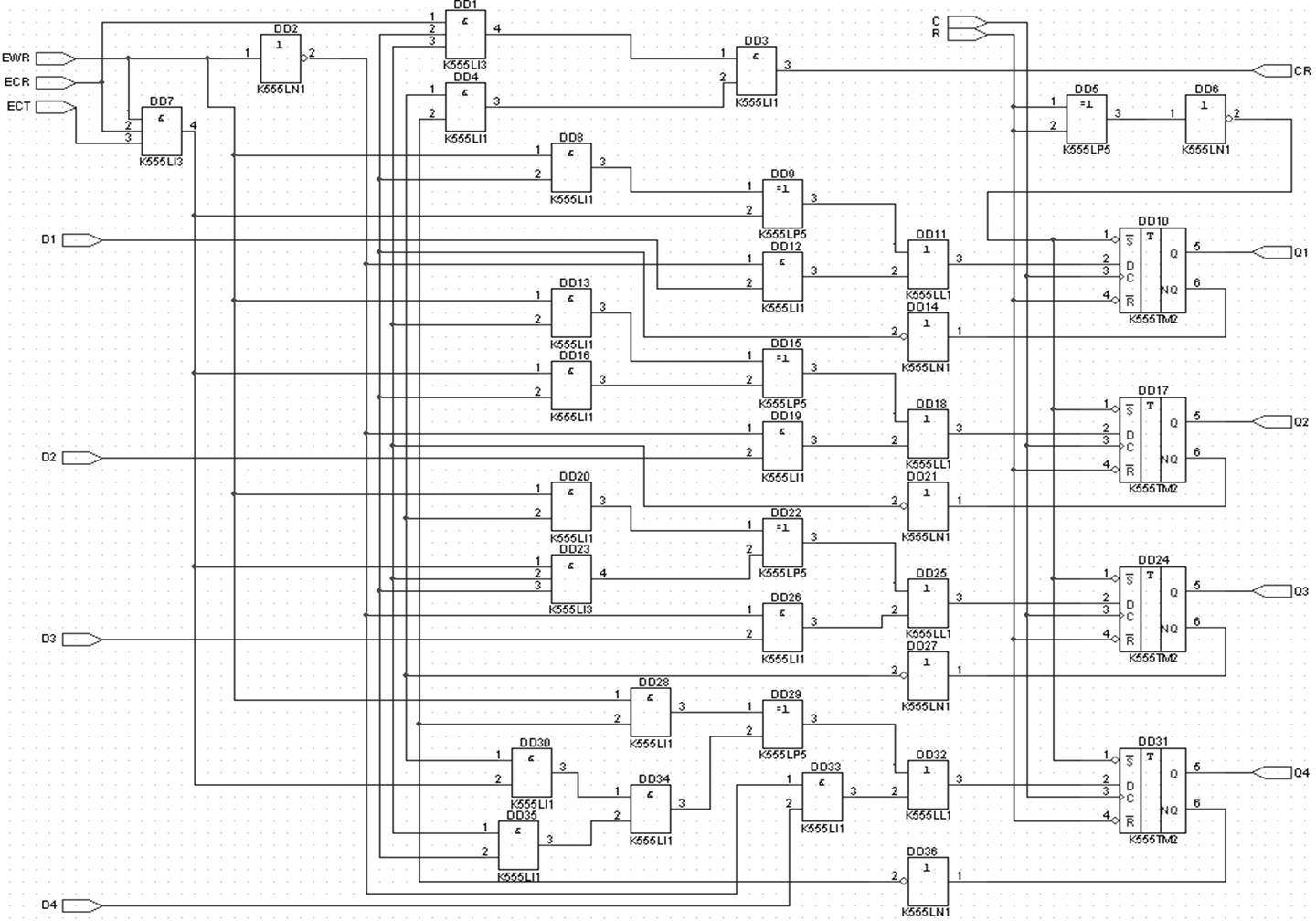

Схема замещения выполнена на спроектированных «с нуля» элементах, в которые заложены задержки, комбинация которых приводит к корректной имитации реального узла ИЕ10.

Принципиальная схема замещения узла приведена на стр. 12 (Рис. 12.).

Рис. 12. Схема замещения иерархического символа (HS1).

Схема верификации иерархического символа (Рис. 13):

Рис. 13. Схема верификации иерархического символа.

![]()

Результаты моделирования узла:

Результаты моделирования узла:

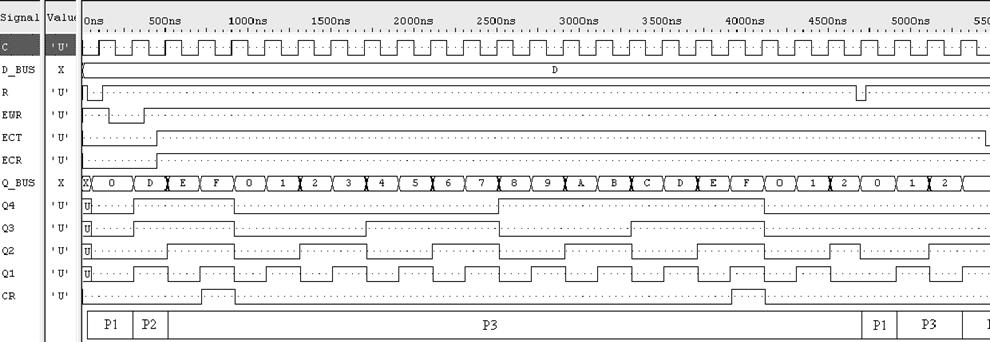

Рис. 14. Временные диаграммы моделируемого узла.

Режимы работы узла (Рис. 14):

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р2 (режим 2) – параллельная загрузка с информационных входов D1-D4 ([Q4,Q3,Q2,Q1]=D).

Р3 (режим 3) – счётный

режим, т.к. все три сигнала ECR, ECT и ![]() имеют высокий уровень.

имеют высокий уровень.

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р3 (режим 3) – счетный режим.

Р4 (режим 4) – хранение, сигнал ECT(вход разрешения счёта) переключается из 1 в 0.

Исследовав основные режимы работы проектируемого узла ИЕ10, и убедившись в правильности работы схемы замещения, можно сделать вывод, что данный элемент успешно выполняет нужные функции. Логика его функционирования совпадает с таблицей функционирования счётчика ИЕ10. После успешного прохождения этапа проверки работы проектируемого узла мы переходим к проверке соответствия временных соотношений в схеме замещения (Рис. 15,16,17).

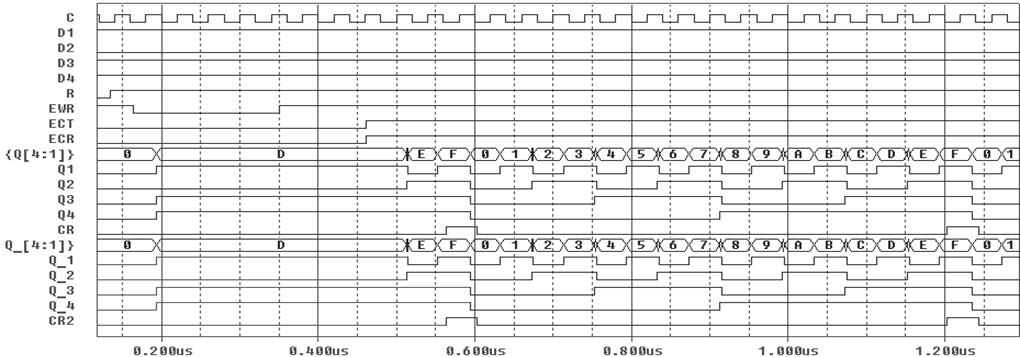

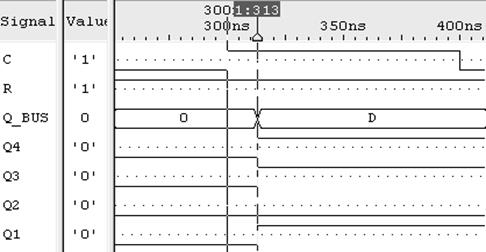

Рис. 15. Задержка распространения сигнала вход cброса

![]() – выход данных Q4,Q3,Q2,Q1 - 26нс.

– выход данных Q4,Q3,Q2,Q1 - 26нс.

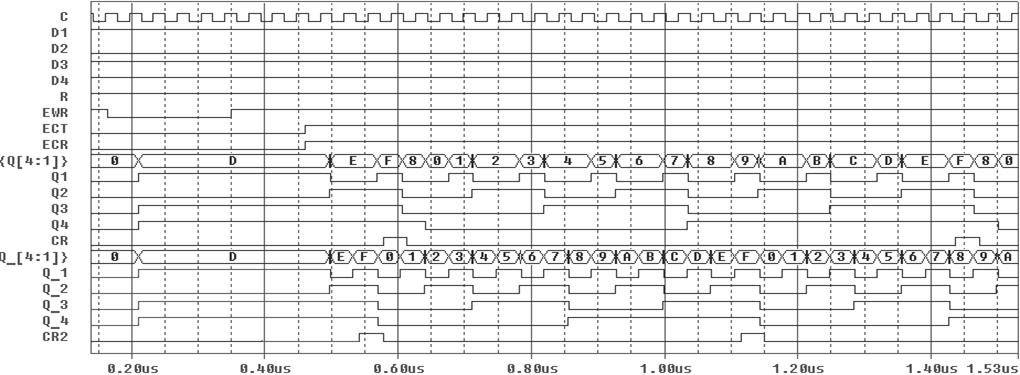

Рис. 16. Время задержки распространения сигнала при включении/выключении:

вход тактирования C – выход

переноса CR - 23нс.

вход тактирования C – выход

переноса CR - 23нс.

Рис. 17. Время задержки распространения сигнала при включении/выключении

Вход тактирования C – выход данных Q4,Q3,Q2,Q1 (включение 13нс, выключение 15нс).

В результате проведенного эксперимента все задержки были имитированы корректно, согласно данным, представленным в оригинальном datasheet компании TexasInstruments.

Заключение:

PCB Simulate проект, как и Spice-проект, показали одинаковые результаты работы. Задержки, заложенные в динамические Pspice-модели вентилей и триггеров схемы замещения иерархического символа были имитированы в PCB Simulate проекте с помощью средств универсального языка описания цифровой аппаратуры VHDL. Именно это решение привело к однозначной работе узла как в Pspice, так и в OrCAD Simulate. Эксперимент в обоих случаях был проведен на одних и тех же входных воздействиях. Качество проделанной работы подтверждается тем, что в обоих случаях узел ведет себя абсолютно одинаково.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

ENTITY K555IE10_V IS PORT(

R, EWR, ECR, ECT : IN std_logic;

D4, D3, D2, D1, C :IN std_logic;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.