|

Max Frequency |

Максимальная частота синхроимпульса |

25 МГц |

Примечание: информация о параметрах узла взята из технической документации, представленной фирмой Texas Insruments (www.ti.com).

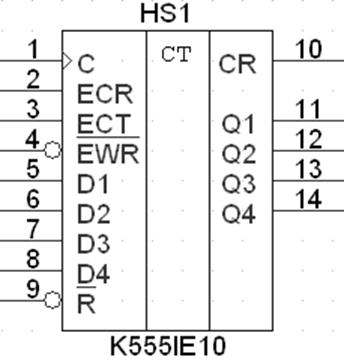

Микросхема

ИЕ10 представляет собой четырёхразрядный двоичный счётчик с асинхронным

сбросом. В микросхеме предусмотрена возможность предварительной записи

информации. Работа ИЕ10 определяется тремя управляющими входами ECT, ECR, ![]() . Низкий уровень напряжения на входе

. Низкий уровень напряжения на входе ![]() разрешает предварительную установку

счётчика в состояние, определяемое логическими уровнями на информационных

входах. Установка проводится синхронно по переднему фронту синхроимпульса.

разрешает предварительную установку

счётчика в состояние, определяемое логическими уровнями на информационных

входах. Установка проводится синхронно по переднему фронту синхроимпульса.

Счёт импульсов, начиная с числа,

предварительно установленного, будет осуществляться только при наличии

напряжения высокого уровня на всех трёх входах управления ECT,

ECR, ![]() .

При напряжении низкого уровня на одном из входов ECT,

ECR на выходах

счётчика сохраняется предыдущее состояние. Установка счётчика в исходное

состояние низкого уровня напряжения на выходах производится асинхронно при

подаче низкого уровня напряжения на вход

.

При напряжении низкого уровня на одном из входов ECT,

ECR на выходах

счётчика сохраняется предыдущее состояние. Установка счётчика в исходное

состояние низкого уровня напряжения на выходах производится асинхронно при

подаче низкого уровня напряжения на вход ![]() .

.

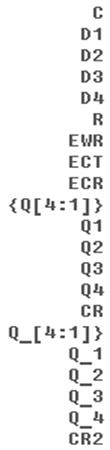

Условное графическое изображение проектируемого узла в виде иерархического символа представлено на Рис. 2.

Рис. 2. Условное графическое изображение узла в виде иерархического символа.

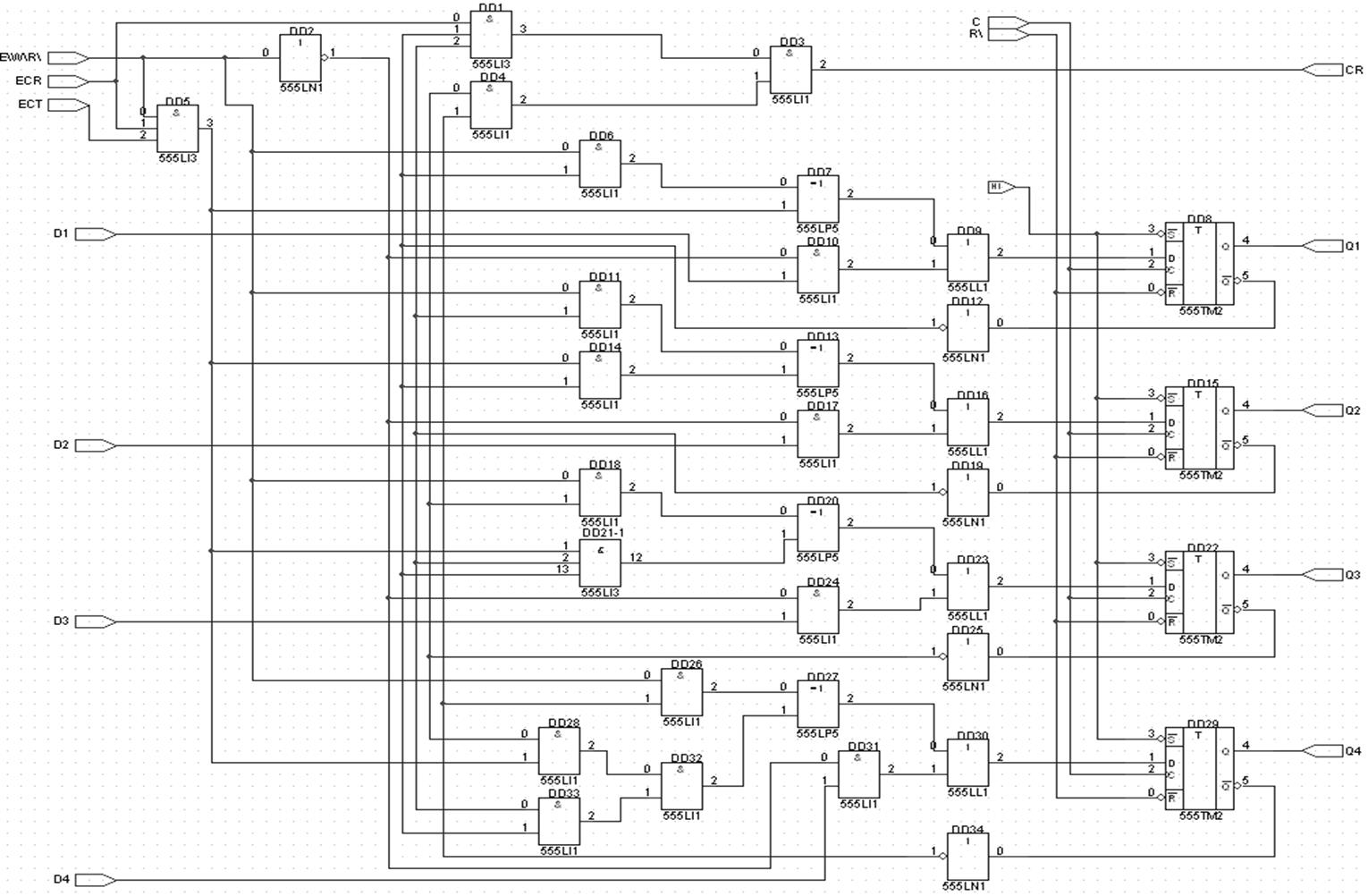

Согласно методическим указаниям к курсовой работе схема замещения проектируемого узла, в данном случае счётчика ИЕ10, должна быть выполнена в отечественных графических обозначениях по ЕСКД. Для этого была создана специальная библиотека символов отечественных компонентов k555ie10.olb.

· Элемент 3И – 555LI3 (зарубежный аналог 74ls11);

· Элемент НЕ – 555LN1 (зарубежный аналог 74ls04);

· Элемент 2И – 555LI1 (зарубежный аналог 74ls08);

· Элемент 2XOR – 555LP5 (зарубежный аналог 74ls86);

· Элемент 2ИЛИ – 555LL1 (зарубежный аналог 74ls32);

· Д-триггер – 555TM2 (зарубежный аналог 74ls74a);

Для схемы замещения потребовались также более сложные элементы: 5И и 4И. Было принято решение не создавать для них специальных символов, поскольку они не имеют однозначных аналогов в сериях отечественных компонентов. Элемент 5И заменён тремя уже разработанными вентилями – (2И + 3И) + 2И = 5И, а элемент 4И: (2И + 2И) + 2И = 4И.

Вышеперечисленные элементы создавались путём редактирования зарубежных компонентов.

Принципиальная схема замещения узла приведена на стр.6.(Рис. 3.)

Рис. 3. Схема замещения иерархического символа HS1.

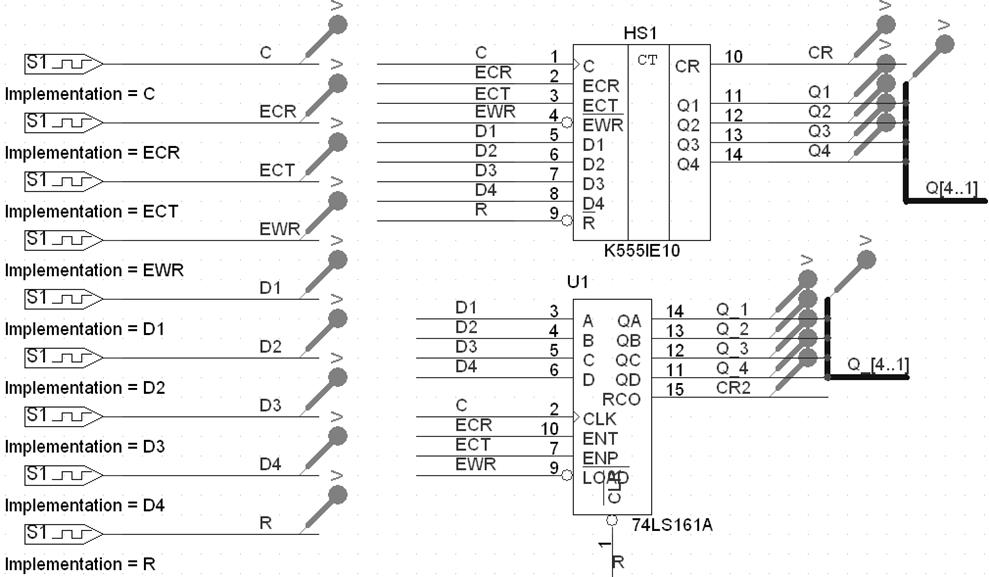

Для более наглядной верификации иерархического символа (HS1) и возможности сравнения с зарубежным аналогом было принято решение добавить в схему верификации зарубежный аналог 74ls161a (U1), взятый из библиотеки 74ls.(Рис. 4 .)

Рис. 4. Схема верификации иерархического символа (HS1) и зарубежного аналога(U1).

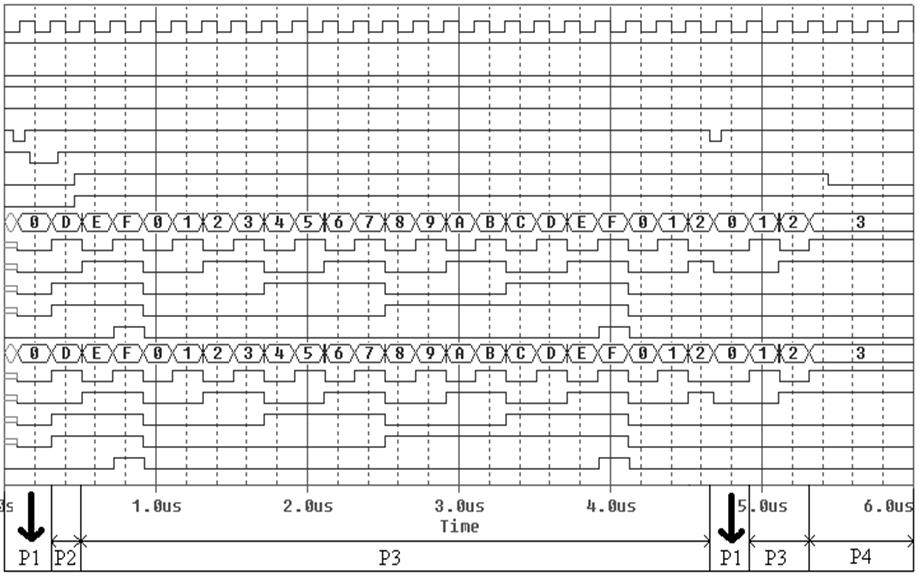

7.4. Результаты

моделирования узла.

7.4. Результаты

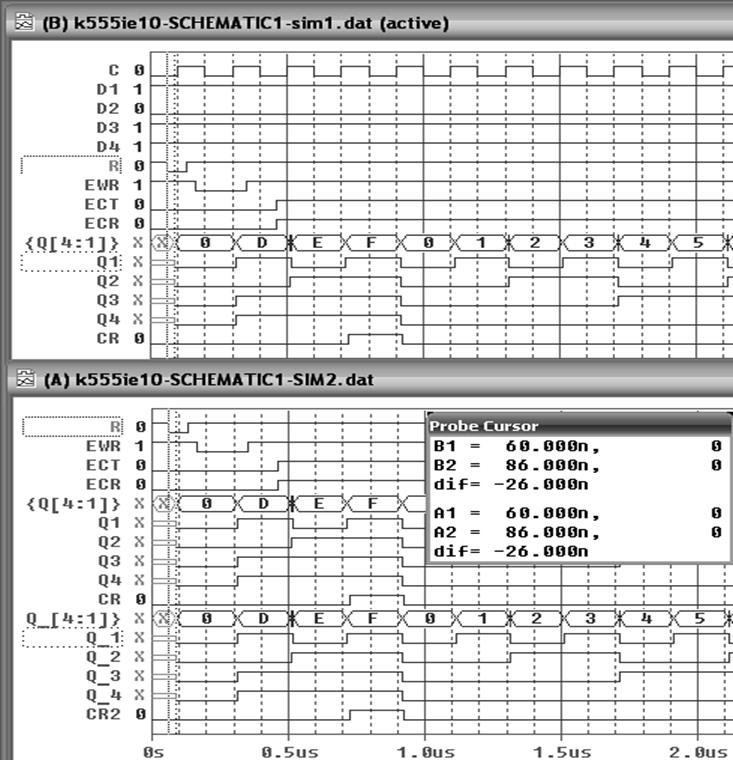

моделирования узла.Рис. 5. Временные диаграммы моделирования иерархического символа (HS1) и его зарубежного аналога(U1).

.

Режимы работы узла (Рис. 5):

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р2 (режим 2) – параллельная загрузка с информационных входов D1-D4 ([Q4,Q3,Q2,Q1]=D).

Р3 (режим 3) – счётный режим, т.к. все три сигнала ECR, ECT и ![]() имеют высокий уровень.

имеют высокий уровень.

Р1 (режим 1) – асинхронный сброс триггеров счетчика в нулевое состояние.

Р3 (режим 3) – счетный режим.

Р4 (режим 4) – хранение, сигнал ECT(вход разрешения счёта) переключается из 1 в 0.

Исследовав основные режимы работы проектируемого узла ИЕ10, и убедившись в правильности работы схемы замещения, можно сделать вывод, что данный элемент успешно выполняет нужные функции. Логика его функционирования совпадает с таблицей функционирования счётчика ИЕ10. После успешного прохождения этапа проверки работы проектируемого узла мы переходим к проверке соответствия временных соотношений в схеме замещения (Рис. 6,7,8).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.