На рис. 12, с помощью временных диаграмм, наглядно представлены следующие режимы работы регистра:

а ) Режим установки логического нуля, который происходит в том случае, если один из входов выбора режима работы ( SEMO0 и SEMO1)

имеют высокий уровень сигнала.

б)Сдвиг вправо. Синхронно осуществляется с прохождением положительного фронта тактового импульса при установке на входе SEMO0 напряжения высокого , а не входе SEMO1 – низкого уровня. В этом режиме даннные последовательно поступают на вход сдвига вправо SR.

Рис. 13 Временная диаграмма работы

VHDL – модели для данного узла.

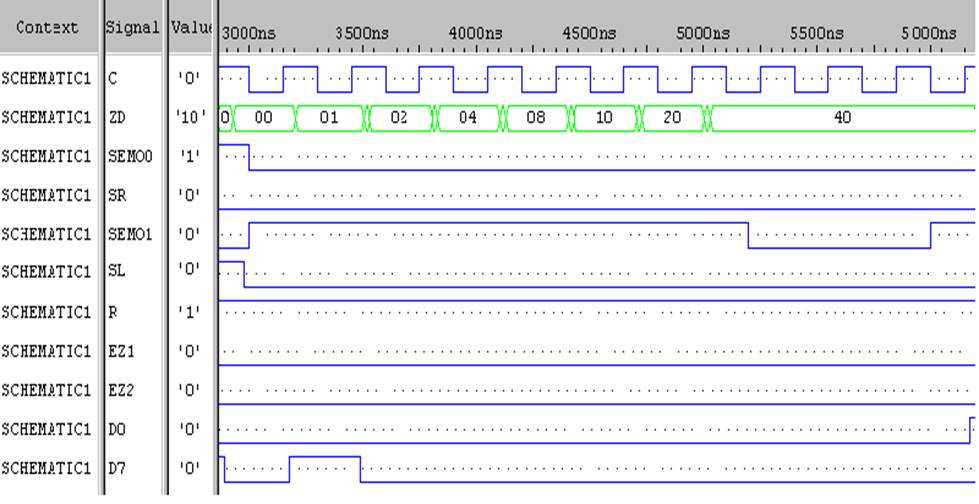

На рис. 13, с помощью временных диаграмм , наглядно представлены следующие режимы работы регистра:

а ) Сдвиг влево. Синхронно осуществляется с прохождением положительного фронта тактового импульса при установке на входе SEMO1 напряжения высокого , а не входе SEMO0 – низкого уровня. В этом режиме даннные последовательно поступают на вход сдвига влево SL

б) режим блокировки (удержания).Реализуется при подаче на оба управляющих входа – SEMO0 и SEMO1 напряжения низкого уровня.

Следует также упомянуть о входах EZ1 и EZ2.

Напряжение высокого уровня на любом из входов EZ1 , EZ2 переводит вход \ выходы в состояние высокого импеданса , но не оказывает при этом влияния на режим работы регистра – параллельную запись , сдвиг вправо или влево , хранение и сброс.

15. Выводы.

Краткая характеристика используемых пакетов.

Пакет PSPICE (DesignLab_8) содержит в себе ряд незаурядных возможностей. Огромный плюс который мне хочется отметить – это возможность задавать временные воздействия непосредственно на графике ,что по сравнению с пакетом OrCAD 9.1 намного удобней . К тому же данный пакет позволяет моделировать цифровые схемы на транзисторном, вентильном и регистровом уровнях.

Пакет OrCAD 9.1 представляет собой более мощный аппарат для проектирования схем как на вентильном, регистровом и процессорном уровнях, так и на системном уровне. Данный пакет содержит язык VHDL - предназначенный для описания аппаратуры высокоскоростных интегральных схем.

Сравнительный анализ.

В Пакетах DesignLab_8 и OrCAD 9.1 содержится большое количество библиотек ; средства, позволяющие посмотреть не только название элемента в библиотеке, но и его функцию (DesignLab_8) и внешний вид; также имеется возможность печати на любом принтере, возможность увеличения/уменьшения изображения, предварительный просмотр (OrCAD).

Оба пакета поддерживают иерархическое проектирование; имеют встроенную поддержку каждый своего языка моделирования: DesignLab_8 – язык HSL, OrCAD 9.1 – язык VHDL.

Мне больше всего понравилось работать в пакете OrCAD, т.к. в нем, на мой взгляд, проще и удобнее рисовать схемы (в этом пакете я рисовал принципиальную схему по «Схемотехнике»), и анализировать полученные результаты (легко менять местами сигналы на временной диаграмме), хотя задавать входные сигналы ,как я упомянул выше , намного проще в пакете DesignLab_8.

16. Список литературы.

1 Шалагинов А.В. Описание лабораторных работ по дисциплине «Моделирование» в пакете PSPICE (DesignLab_8).

2 Шалагинов А.В. Описание лабораторных работ по дисциплине «Моделирование» в пакете OrCAD 9.1.

3 Петровский И.И. и др. Логические ИС КР1533, КР1554: Справочник: В 2 ч. – М.: Фирма «МИКАП», 1993. – Ч.1. – 158 с.

4 Шило А.Н. «Справочник по цифровой электронике».

5 Шалагинов А.В. Цифровое моделирование в САПР DesignLab_8.Уроки для beginner’a. Учебное пособие. - Новосибирск : Изд – во НГТУ, 2000 – 87 с.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.