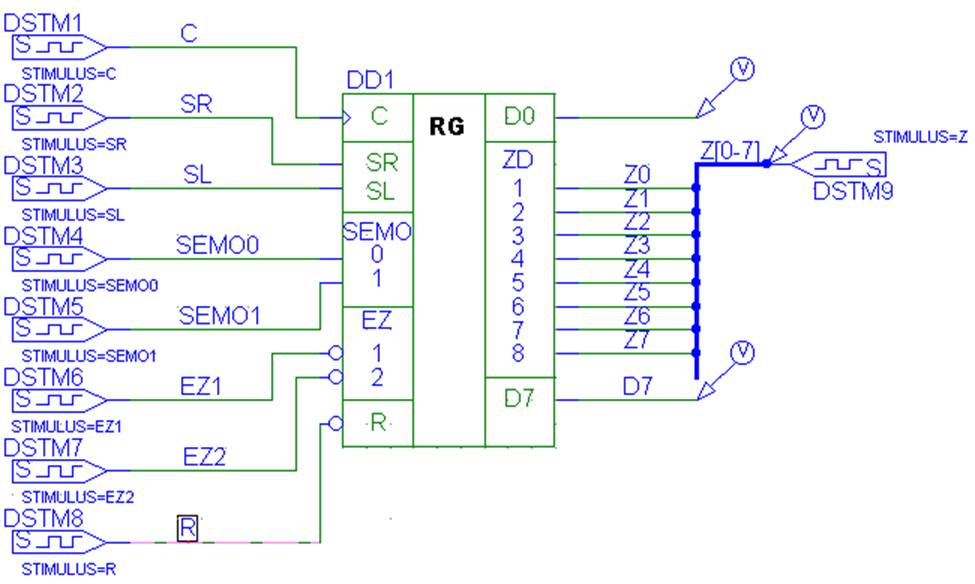

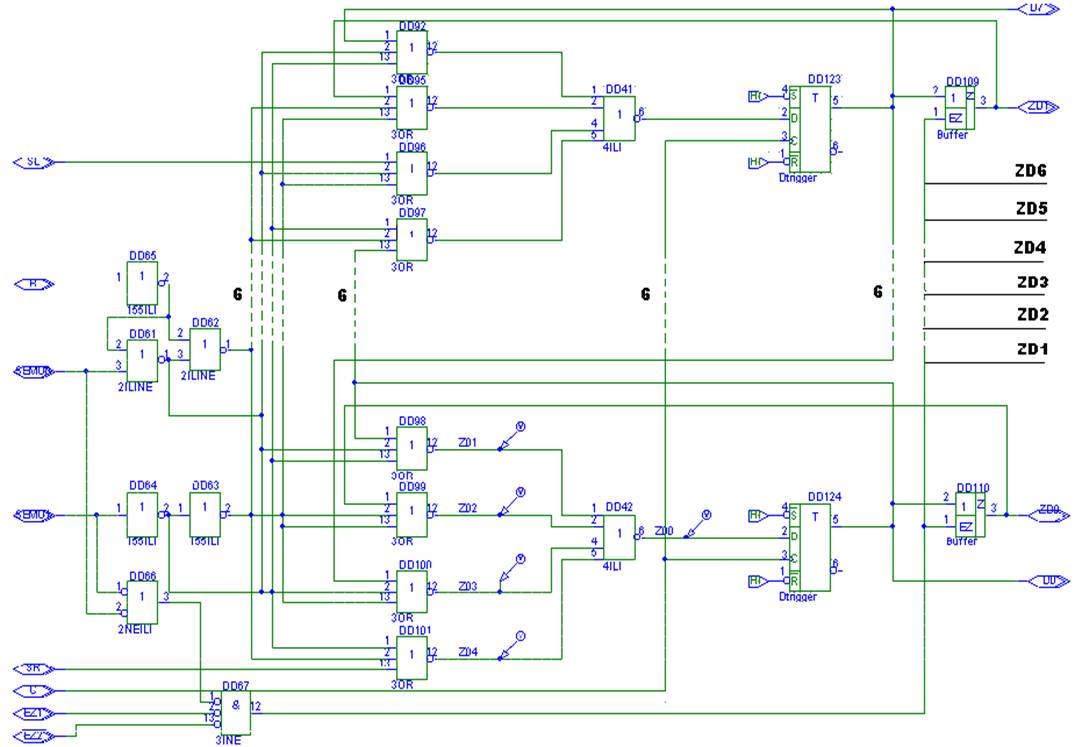

4.Моделирование регистра ИР29 в пакете DesignLab.

1.Принципиальная схема проектируемого узла и его внутреннее описание, созданные в графическом редакторе Schematics.

|

Рис. 3. Внутреннее описание узла.

5. Текстовое SPICE-описание моделируемого узла

(содержимое файлов *.cir и *.net).

*.cir

* C:\Akurs\register.sch

* Schematics Version 8.0 - July 1997

* Mon Dec 10 22:03:16 2001

** Analysis setup **

.tran 20ns 10000ns

.INC "C:\MSim_8\UserLib\My1.lib"

.INC "C:\Akurs\register.stl"

.STMLIB "C:\Akurs\register.stl"

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "C:\Akurs1\register.lib"

.lib "nom.lib"

.INC "register.net"

.INC "register.als"

.probe

.END

*Net

* Schematics Netlist *

U_DSTM10 STIM(8,0) $G_DPWR $G_DGND Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7 IO_STM

+ STIMULUS=Z

U_DSTM6 STIM(1,0) $G_DPWR $G_DGND EZ1 IO_STM STIMULUS=EZ1

U_DSTM4 STIM(1,0) $G_DPWR $G_DGND SEMO0 IO_STM STIMULUS=SEMO0

U_DSTM8 STIM(1,0) $G_DPWR $G_DGND R IO_STM STIMULUS=R

U_DSTM2 STIM(1,0) $G_DPWR $G_DGND SR IO_STM STIMULUS=SR

U_DSTM5 STIM(1,0) $G_DPWR $G_DGND SEMO1 IO_STM STIMULUS=SEMO1

U_DSTM7 STIM(1,0) $G_DPWR $G_DGND EZ2 IO_STM STIMULUS=EZ2

X_DD1_DD37 $N_0006 $N_0007 $N_0008 $N_0009 $N_0005 $G_DPWR $G_DGND 4ILI

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD38 $N_0011 $N_0012 $N_0013 $N_0014 $N_0010 $G_DPWR $G_DGND 4ILI

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD39 $N_0016 $N_0017 $N_0018 $N_0019 $N_0015 $G_DPWR $G_DGND 4ILI

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD40 $N_0021 $N_0022 $N_0023 $N_0024 $N_0020 $G_DPWR $G_DGND 4ILI

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD41 $N_0026 $N_0027 $N_0028 $N_0029 $N_0025 $G_DPWR $G_DGND 4ILI

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD42 DD1_Z01 DD1_Z02 DD1_Z03 DD1_Z04 DD1_Z00 $G_DPWR $G_DGND 4ILI

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD61 $N_0030 SEMO0 $N_0031 $G_DPWR $G_DGND 2ILINE PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD62 $N_0030 $N_0031 $N_0032 $G_DPWR $G_DGND 2ILINE PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD63 $N_0033 $N_0034 $G_DPWR $G_DGND ILI PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD64 SEMO1 $N_0033 $G_DPWR $G_DGND ILI PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD66 SEMO1 SEMO0 $N_0035 $G_DPWR $G_DGND 2NEILI PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD68 D7 $N_0031 $N_0033 $N_0036 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD69 Z7 $N_0032 $N_0034 $N_0037 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD70 SL $N_0031 $N_0034 $N_0038 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD71 $N_0033 $N_0032 $N_0040 $N_0039 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD72 $N_0040 $N_0031 $N_0033 $N_0041 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD73 Z6 $N_0032 $N_0034 $N_0042 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD77 Z5 $N_0032 $N_0034 $N_0007 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD81 Z4 $N_0032 $N_0034 $N_0012 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD82 $N_0043 $N_0031 $N_0034 $N_0013 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD85 Z3 $N_0032 $N_0034 $N_0017 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD86 $N_0044 $N_0031 $N_0034 $N_0018 $G_DPWR $G_DGND 3OR PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.