+

+ PINDLY:

+ D0_O D7_O = {

+ CASE(

+ CLOCK & TRN_LH, DELAY(5NS,-1,15NS),

+ CLOCK & TRN_HL, DELAY(8NS,-1,18NS),

+ CHANGED(CLRBAR,0) & TRN_HL, DELAY(6NS,-1,22NS),

+ DELAY(9NS,-1,23NS) ;DEFAULT

+ )

+ }

+

+ TRISTATE:

+ ENABLE LO OE

+ ZD0_B ZD1_B ZD2_B ZD3_B ZD4_B ZD5_B ZD6_B ZD7_B = {

+ CASE(

+ ENABLE1 & TRN_ZH, DELAY(6NS,-1,16NS),

+ ENABLE2 & TRN_ZH, DELAY(7NS,-1,17NS),

+ ENABLE1 & TRN_ZL, DELAY(8NS,-1,22NS),

+ ENABLE2 & TRN_ZL, DELAY(8NS,-1,22NS),

+ DISABLE1 & TRN_HZ, DELAY(1NS,-1,8NS),

+ DISABLE2 & TRN_HZ, DELAY(1NS,-1,12NS),

+ DISABLE1 & TRN_LZ, DELAY(5NS,-1,15NS),

+ DISABLE2 & TRN_LZ, DELAY(8NS,-1,25NS),

+ CLOCK & TRN_LH, DELAY(4NS,-1,13NS),

+ CLOCK & TRN_HL, DELAY(7NS,-1,19NS),

+ CHANGED(CLRBAR,0) & TRN_HL, DELAY(6NS,-1,22NS),

+ DELAY(9NS,-1,26NS) ;DEFAULT

+ )

+ }

+

+ FREQ:

+ NODE = C

+ MAXFREQ = 30MEG

+

+ WIDTH:

+ NODE = C

+ MIN_HI = 16.5NS

+ MIN_LO = 16.5NS

+

+ SETUP_HOLD:

+ DATA(1) = CLRBAR

+ CLOCK LH = C

+ SETUPTIME_LO = 20NS

+ SETUPTIME_HI = 16NS

+

+ SETUP_HOLD:

+ DATA(2) = SEMO1 SEMO0

+ CLOCK LH = C

+ SETUPTIME = 20NS

+ WHEN = { CLRBAR!='0 }

+

+ SETUP_HOLD:

+ DATA(8) = ZD0 ZD1 ZD2 ZD3 ZD4 ZD5 ZD6 ZD7

+ CLOCK LH = C

+ SETUPTIME_HI = 16NS

+ SETUPTIME_LO = 6NS

+ WHEN = { CLRBAR!='0

+ & (SEMO1!='0 ^ CHANGED(SEMO1,0)) & (SEMO0!='0 ^ CHANGED(SEMO0,0)) }

+

+ SETUP_HOLD:

+ DATA(1) = SL

+ CLOCK LH = C

+ SETUPTIME_HI = 16NS

+ SETUPTIME_LO = 6NS

+ WHEN = { CLRBAR!='0

+ & (SEMO1!='0 ^ CHANGED(SEMO1,0)) & (SEMO0!='1 ^ CHANGED(SEMO0,0)) }

+

+ SETUP_HOLD:

+ DATA(1) = SR

+ CLOCK LH = C

+ SETUPTIME_HI = 16NS

+ SETUPTIME_LO = 6NS

+ WHEN = { CLRBAR!='0

+ & (SEMO1!='1 ^ CHANGED(SEMO1,0)) & (SEMO0!='0 ^ CHANGED(SEMO0,0)) }

*

.ENDS

*

*$

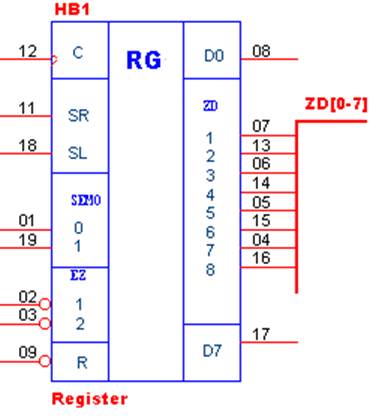

Моделирование регистра ИР29 в пакете OrCAD 9.1

|

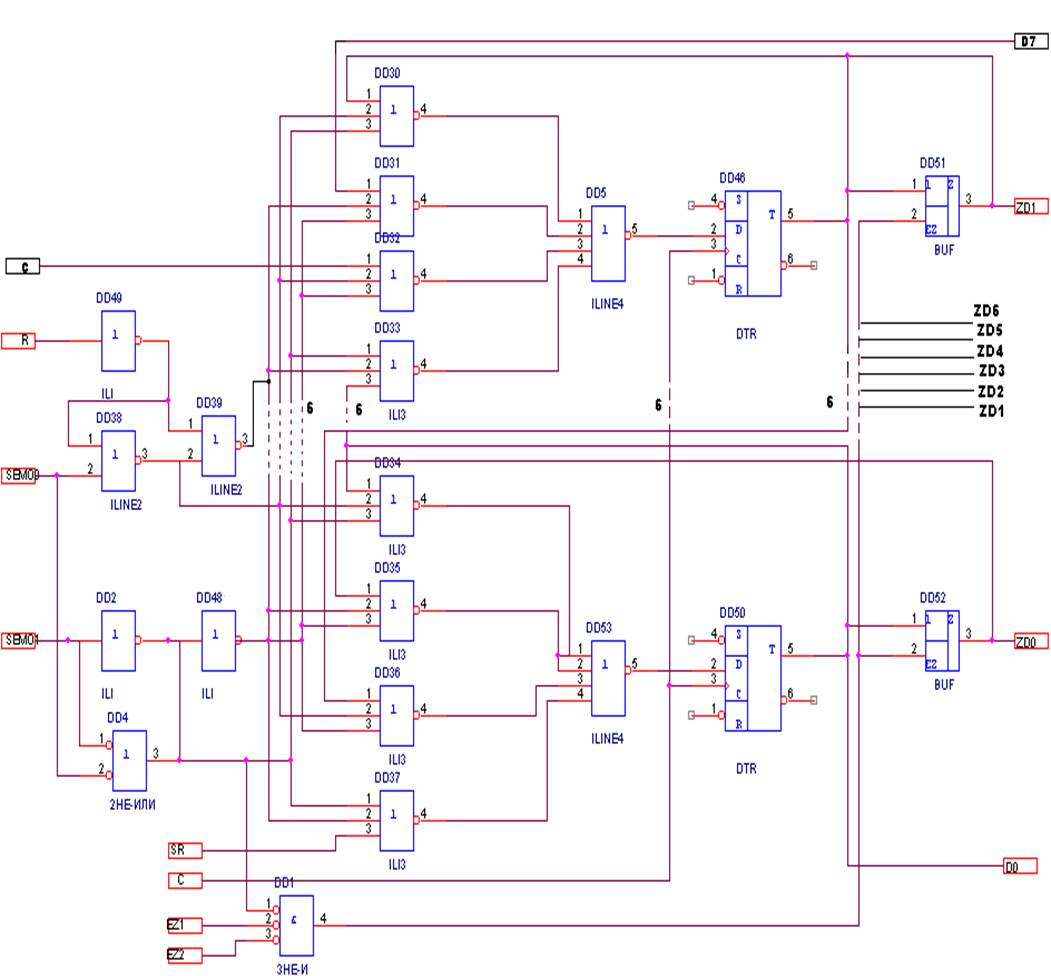

Рис 8. Внутреннее описание проектируемого узла.

11. Результаты моделирования узла в пакете OrCAD 9.1

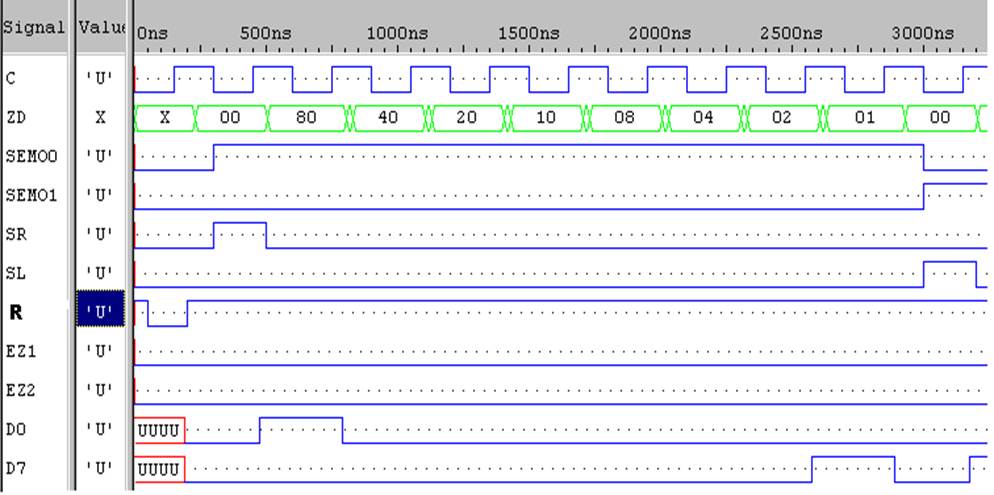

Рис 9 Установка “Логический 0” и сдвиг вправо.

На рис. 9, с помощью временных диаграмм, наглядно представлены следующие режимы работы регистра:

а ) Режим установки логического нуля, который происходит в том случае, если один из входов выбора режима работы ( SEMO0 и SEMO1)

имеют высокий уровень сигнала.

б)Сдвиг вправо. Реализуется после активизации SR (входа разрешения “сдвига вправо”) и высокого уровня SEMO0.

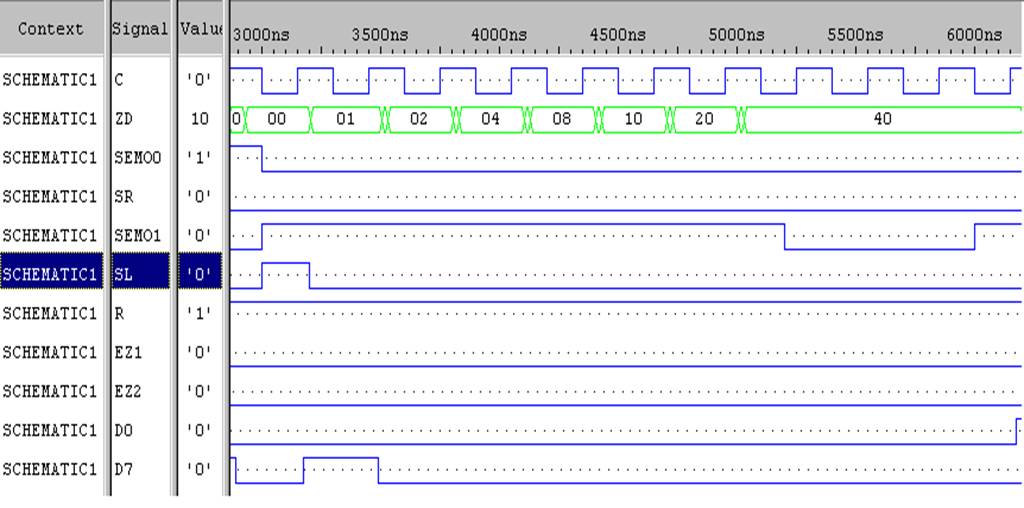

Рис. 10.Сдвиг влево.

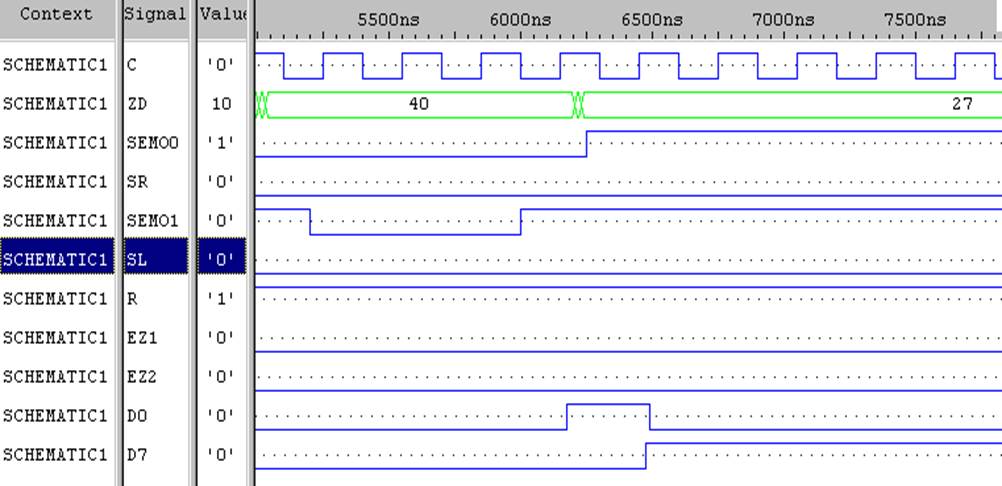

На рис. 10, с помощью временных диаграмм, наглядно представлены следующие режимы работы регистра:

а ) Сдвиг влево. Реализуется после активизации SL(входа разрешения “сдвига вправо”), установки SEMO0 в нуль, и высокого уровня SEMO1.

б) Режим удержания ( 40 )

Рис 11.Режим загрузки.

На рис. 11, с помощью временных диаграмм , наглядно представлен режим загрузки (27).

12. Поведенческая VHDL- модель узла.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.NUMERIC_STD.all;

entity \register\ is

port(C,SR,SL,SEMO0,SEMO1,EZ1,EZ2,R : in std_logic;

D0,D7 : out std_logic;

ZD0,ZD1,ZD2,ZD3,ZD4,ZD5,ZD6,ZD7 :inout std_logic);

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.