МО и ПО

РФ

НГТУ

Курсовая работа по

Моделированию.

Факультет: АВТ

Группа: АМ – 89

Студент: Бобров Д.В.

Преподаватель: Шалагинов A. В.

2001 г.

Содержание

1.Постановка задачи . 3

2.Описание . 4

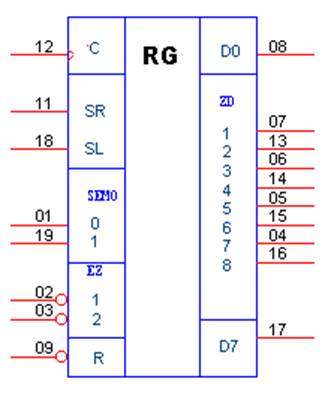

3. Условно-графическое обозначение . 4

Таблица назначений выводов . 5

Таблица истинности 1,2 6

Таблица реальных задержек 7

4. Моделирование регистра ИР29 в пакете DesignLab_8 8

5. Текстовое описание. 10

6. Содержание файла описания внешних воздействий. 14

7. Временные диаграммы. 16

8. Оценка предельных скоростных возможностей узла. 18

10. Моделирование регистра ИР в пакете OrCAD 9.1 :

Принципиальная схема проектируемого узла и его внутреннее описание . 22 – 23

11. Результаты моделирования узла в пакете OrCAD 9.1 . 24

12. Поведенческая VHDL - моделируемого узла . 27

13. Файл , содержащий список цепей . 28

14. Результаты верификации VHDL – модели. 29

15. Выводы :

- Краткая характеристика используемых пакетов 31

- Сравнительный анализ 32

16.Список литературы . 32

Исследовать возможности различных систем моделирования на примере построения конкретной модели, провести сравнительный анализ построенных и верифицированных моделей.

Получить практические навыки работы с системой автоматизированного проектирования электронной аппаратуры

Используя пакет DesignLab_8:

1) Создать иерархический символ, внутреннее описание которого представлено в виде схемы замещения проектируемого узла.

2) Создать Pspice – модель данного символа и провести моделирование.

Используя пакет OrCAD 9.1:

1) Создать иерархический символ, внутреннее описание которого представлено в виде схемы замещения проектируемого узла.).

2) Провести оценку предельных скоростных возможностей исследуемого узла.

Используя язык VHDL:

1) Создать поведенческую VHDL-модель узла с реальными задержками.

2) Провести её верифицирование. Добиться максимальной идентичности с задержками, измеренными на принципиальной схеме узла.

2.Описание узла.

В качестве исследуемого узла взят элемент ИР29 реализованный на серии КР 1533.

Этот элемент представляет собой 8-разрядный универсальный сдвиговый регистр с выходом на три состояния и может применяться в качестве буферного запоминающего устройства для временного хранения данных, для преобразования данных из параллельной формы в последовательную и наоборот, или для задержки информационных сигналов. Широко используется в микропроцессорных системах.

Данный регистр объединяет возможные характеристики регистров сдвига. Данные могут сдвигаться влево и вправо. Предусмотрен режим хранения (останова). Данный регистр может работать в четырёх режимах:

- сдвиг вправо (от D0 к D7);

- сдвиг влево (от D7 к D0);

- параллельная загрузка;

- удержание.

Синхронная параллельная загрузка осуществляется путём установки напряжения высокого уровня на управляющие входы SEM00,SEM01.

|

Рис 1.Условно – графическое изображение.

Таблица 1

Таблица назначения выводов.

|

Номер контакта |

Мнемоника |

Назначение |

|

1 |

SEM00 |

Вход выбора режима работы |

|

2 |

EZ1 |

Вход разрешения состояния высокого импеданса |

|

3 |

EZ2 |

Вход разрешения состояния высокого импеданса |

|

4 |

ZD6 |

Вход/выход данных |

|

5 |

ZD4 |

Вход/ выход данных |

|

6 |

ZD2 |

Вход/ выход данных |

|

7 |

ZD0 |

Вход/выход данных |

|

8 |

D0 |

Выход первого разряда данных |

|

9 |

R |

Вход установки в состояние “логический 0” |

|

10 |

OV |

Общий вывод |

|

11 |

SR |

Вход “сдвиг вправо” |

|

12 |

C |

Вход тактовый |

|

13 |

ZD1 |

Вход/ выход данных |

|

14 |

ZD3 |

Вход/ выход данных |

|

15 |

ZD5 |

Вход/ выход данных |

|

16 |

ZD7 |

Вход/ выход данных |

|

17 |

D7 |

Выход восьмого разряда данных |

|

18 |

SL |

Выход “сдвиг влево” |

|

19 |

SEMOT |

Вход выбора режима |

|

20 |

Ucc |

Вывод питания от источника напряжения |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.