end \register\;

architecture MODEL of \register\ is

SIGNAL W: std_logic_vector(0 TO 7);

SIGNAL DD: std_logic_vector(0 TO 7);

SIGNAL D_0 : STD_LOGIC;

SIGNAL D_7 : STD_LOGIC;

begin

PROCESS (C,SL,SR,R,SEMO0,SEMO1)

BEGIN

IF (R='1') THEN

IF (EZ1='0' AND EZ2='0')THEN

IF (SEMO0='1' AND SEMO1='0' AND C='1' AND C'EVENT) THEN

DD <= DD srl 1;

D_0<=SR;

IF (SR='1') THEN

DD(0)<='1';

END IF;

D_7<=DD(7);

W <= DD;

ELSIF (SEMO0='0'AND SEMO1='1' AND C'EVENT AND C='1')THEN DD <= DD sll 1;

D_7<=SL;

IF (SL='1') THEN

DD(7)<='1';

END IF;

D_7<=W(7);

W<=DD;

END IF;

END IF;

IF(SEMO0='1' AND SEMO1='1'AND C'EVENT AND C='1') THEN

DD<=(ZD0,ZD1,ZD2,ZD3,ZD4,ZD5,ZD6,ZD7);

W<=DD;

END IF;

ELSE

DD<=('0','0','0','0','0','0','0','0');

IF(SEMO0='1' AND SEMO1='1') THEN

W<=('Z','Z','Z','Z','Z','Z','Z','Z');

ELSIF(EZ1='0' AND EZ2='0') THEN

W<=DD;

END IF;

END IF;

END PROCESS;

D0<=D_0 AFTER 45 ns;

D7<=D_7 AFTER 45ns;

(ZD0,ZD1,ZD2,ZD3,ZD4,ZD5,ZD6,ZD7) <= W AFTER 45ns;

end MODEL;

13. Файл, содержащий список цепей.

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY SCHEMATIC1 IS END SCHEMATIC1;

ARCHITECTURE STRUCTURE OF SCHEMATIC1 IS

-- COMPONENTS

COMPONENT IR29

PORT (

D0 : OUT std_logic;

ZD0 : INOUT std_logic;

ZD1 : INOUT std_logic;

ZD2 : INOUT std_logic;

ZD3 : INOUT std_logic;

ZD4 : INOUT std_logic;

ZD5 : INOUT std_logic;

ZD6 : INOUT std_logic;

ZD7 : INOUT std_logic;

C : IN std_logic;

SL : IN std_logic;

SR : IN std_logic;

SEMO0 : IN std_logic;

SEMO1 : IN std_logic;

EZ1 : IN std_logic;

EZ2 : IN std_logic;

R : IN std_logic;

D7 : OUT std_logic

); END COMPONENT;

-- SIGNALS

SIGNAL C : std_logic;

SIGNAL SEMO0 : std_logic;

SIGNAL SL : std_logic;

SIGNAL SR : std_logic;

SIGNAL R : std_logic;

SIGNAL D7 : std_logic;

SIGNAL EZ1 : std_logic;

SIGNAL EZ2 : std_logic;

SIGNAL SEMO1 : std_logic;

SIGNAL D0 : std_logic;

SIGNAL ZD : std_logic_vector(0 TO 7);

-- INSTANCE ATTRIBUTES

-- GATE INSTANCES

BEGIN

DD2 : IR29 PORT MAP(

D0 => D0,

ZD0 => ZD(0),

ZD1 => ZD(1),

ZD2 => ZD(2),

ZD3 => ZD(3),

ZD4 => ZD(4),

ZD5 => ZD(5),

ZD6 => ZD(6),

ZD7 => ZD(7),

C => C,

SL => SL,

SR => SR,

SEMO0 => SEMO0,

SEMO1 => SEMO1,

EZ1 => EZ1,

EZ2 => EZ2,

R => R,

D7 => D7

);

END STRUCTURE;

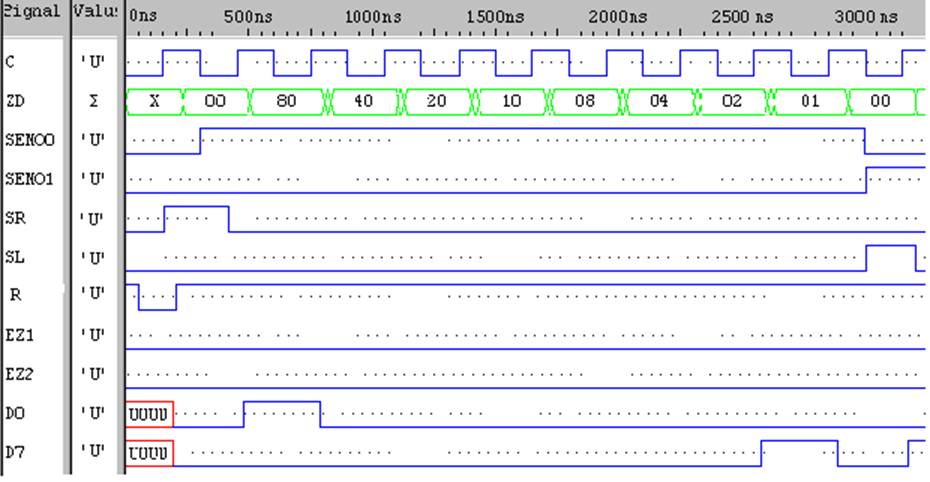

14. Результаты верификации VHDL – модели.

Рис. 12 Временная диаграмма работы

VHDL – модели для данного узла.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.