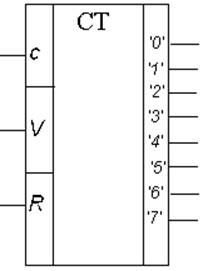

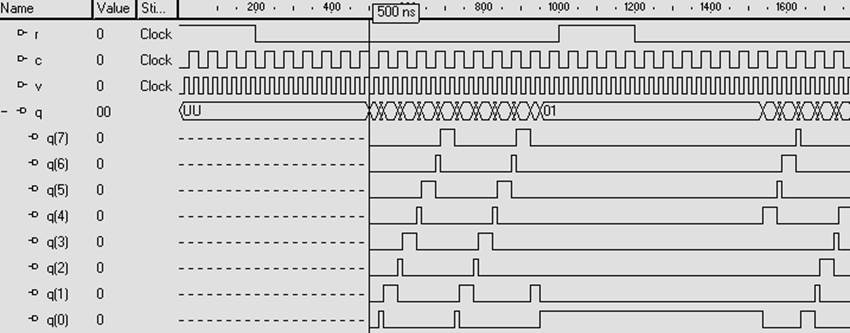

Условное обозначение K561ИЕ9

Задержка 500 нс.

Таблица истинности элемента К561ИЕ9

1.11 Микросхема К561ИЕ10.

Данная микросхема представляет собой два четырёхразрядных счётчика, находящихся в одном корпусе. Содержит 354 интегральных элемента.

|

C |

V |

R |

Операции |

|

|

1 |

0 |

Счёт |

|

0 |

|

0 |

Счёт |

|

|

‘X’ |

0 |

Нет счёта |

|

‘X’ |

|

0 |

Нет счёта |

|

|

0 |

0 |

Нет счёта |

|

1 |

|

0 |

Нет счёта |

|

‘X’ |

‘X’ |

1 |

Q(i):=0 |

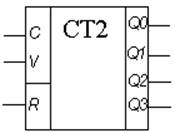

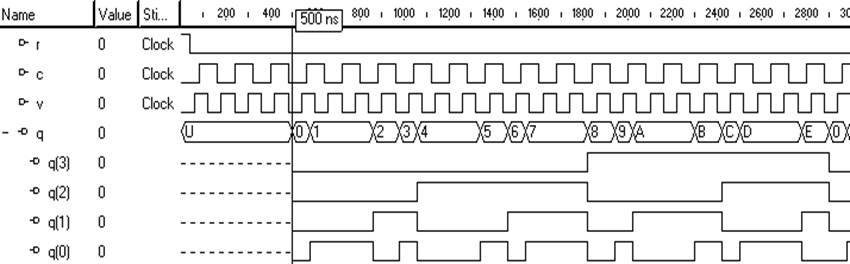

Условное обозначение K561ИЕ10

Задержка 500 нс.

Таблица истинности элемента К561ИЕ10

1.12 Микросхема К561ИЕ11.

Данная микросхема представляет собой четырехразрядный двоичный реверсивный счётчик, содержит 319 интегральных элементов.

|

P0 |

|

V |

R |

Действие |

|

1 |

‘X’ |

0 |

0 |

Нет счёта |

|

0 |

1 |

0 |

0 |

Работа на сложение |

|

0 |

0 |

0 |

0 |

Работа на вычитание |

|

'X' |

‘X’ |

1 |

0 |

Установка |

|

‘X’ |

‘X’ |

‘X’ |

1 |

Установка нуля |

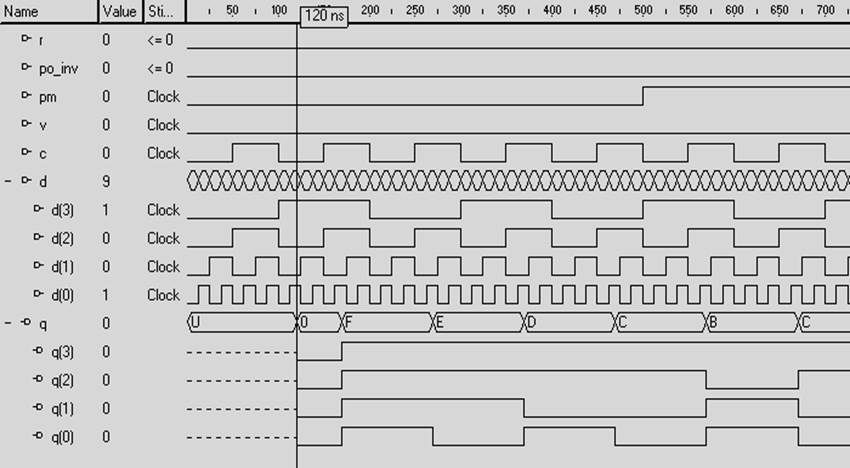

Условное обозначение K561ИЕ11 Таблица истинности элемента К561ИЕ11

Задержка 120 нс.

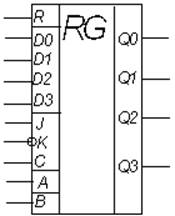

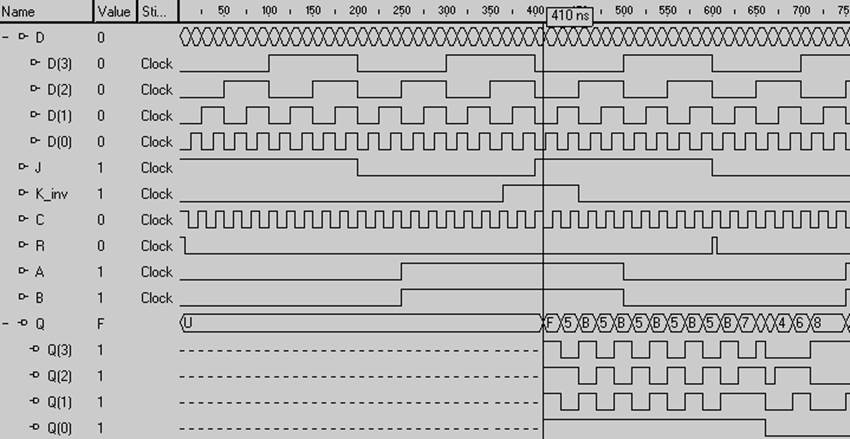

1.13 Микросхема К561ИР9.

Данная микросхема представляет собой четырехразрядный последовательно параллельный регистр. Содержит 207 интегральных элементов.

|

C |

J |

|

R |

Q(i-1) |

Q(i) |

|

|

0 |

‘X’ |

0 |

0 |

0 |

|

|

1 |

‘X’ |

0 |

0 |

1 |

|

|

‘X’ |

0 |

0 |

1 |

0 |

|

|

1 |

0 |

0 |

Q(i-1) |

|

|

|

‘X’ |

1 |

0 |

1 |

1 |

|

|

‘X’ |

‘X’ |

0 |

Q(i-1) |

Q(i-1) |

|

|

‘X’ |

‘X’ |

1 |

‘X’ |

0 |

Условное обозначение K561ИР9 Задержка 410 нс. Таблица истинности элемента К561ИР9

2. Моделирование.

2.1 Моделирование элементов схемы.

K514id2

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity k514id2 is

port(

d:in STD_LOGIC_VECTOR(3 downto 0);

q:out std_logic_vector(6 downto 0)

);

end k514id2;

architecture k514id2 of k514id2 is

begin

process(d)

begin

case d is

when "0000"=>q<=transport"1111111"after 24ns;

when "1000"=>q<=transport"0110000"after 24ns;

when "0100"=>q<=transport"1101101"after 24ns;

when "1100"=>q<=transport"1111001"after 24ns;

when "0010"=>q<=transport"0110011"after 24ns;

when "1010"=>q<=transport"1011011"after 24ns;

when "0110"=>q<=transport"1011111"after 24ns;

when "1110"=>q<=transport"1110000"after 24ns;

when "0001"=>q<=transport"1111111"after 24ns;

when "1001"=>q<=transport"1111011"after 24ns;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.