port map(D(0)=>sg33,D(1)=>sg28,D(2)=>sg32,D(3)=>sg34,J=>sg52,

K_inv=>sg52,C=>sg20,R=>'0',A=>sg50,B=>k18,q(2)=>sg53,

q(0)=>sg90,q(1)=>sg90,q(3)=>sg90);

dd14:k561ir9

port map(D(0)=>sg37,D(1)=>sg35,D(2)=>sg36,D(3)=>sg38,J=>sg53,

K_inv=>sg53,C=>sg20,R=>'0',A=>sg50,B=>k18,q(2)=>sg57,

q(0)=>sg90,q(1)=>sg90,q(3)=>sg90);

dd19:k561ir9

port map(D(0)=>k2,D(1)=>k2,D(2)=>k2,D(3)=>k2,J=>sg54,

K_inv=>sg54,C=>sg20,R=>'0',A=>sg50,B=>k18,q(2)=>sg49,

q(0)=>sg90,q(1)=>sg90,q(3)=>sg90);

dd20:k561ir9

port map(D(0)=>k2,D(1)=>k2,D(2)=>k2,D(3)=>k2,J=>sg55,

K_inv=>sg55,C=>sg20,R=>'0',A=>sg50,B=>k18,q(2)=>sg49,

q(0)=>sg90,q(1)=>sg90,q(3)=>sg90);

dd25:k561ir9

port map(D(0)=>sg42,D(1)=>sg39,D(2)=>sg41,D(3)=>sg43,J=>sg56,

K_inv=>sg56,C=>sg20,R=>'0',A=>sg50,B=>k18,q(3)=>sg55,

q(0)=>sg86,q(1)=>sg87,q(2)=>sg88);

dd26:k561ir9

port map(D(0)=>sg45,D(1)=>sg40,D(2)=>sg44,D(3)=>sg46,J=>sg57,

K_inv=>sg57,C=>sg20,R=>'0',A=>sg50,B=>k18,q(2)=>sg56,

q(0)=>sg90,q(1)=>sg90,q(3)=>sg90);

dd16_1:k561lp13

port map(sg12,sg19,sg58,sg59);

dd16_2:k561lp13

port map(sg60,sg3,'0',sg50);

dd16_3:k561lp13

port map(sg60,sg3,'0',sg8);

dd17:k561ie9

port map(r=>'0',c=>sg16,v=>'0',q(0)=>sg60,q(1)=>sg61,q(2)=>sg62,

q(3)=>sg63,q(4)=>sg64,q(5)=>sg65,q(6)=>sg58,q(7)=>sg66);

dd18:k561ie8

port map(r=>'0',c1=>sg66,c2_inv=>sg11,q(0)=>sg3,q(1)=>sg17,

q(2)=>sg90,q(3)=>sg90,q(4)=>sg90,q(5)=>sg90,q(6)=>sg90,

q(7)=>sg90,q(8)=>sg90,q(9)=>sg90);

dd27_1:k561tm3

port map(d=>sg86,c=>sg16,r=>k18,s=>k18,q=>sg77);

dd27_2:k561tm3

port map(d=>sg87,c=>sg16,r=>k18,s=>k18,q=>sg77);

dd27_3:k561tm3

port map(d=>sg88,c=>sg16,r=>k18,s=>k18,q=>sg77);

dd27_4:k561tm3

port map(d=>sg55,c=>sg16,r=>k18,s=>k18,q=>sg77);

dd23_1_a:k561ln1

port map(sg60,'0','0',sg67);

dd23_1_b:k561ln1

port map(sg61,'0','0',sg68);

dd23_1_c:k561ln1

port map(sg2,'0','0',sg69);

dd23_1_d:k561ln1

port map(sg65,'0','0',sg70);

dd23_1_e:k561ln1

port map(sg58,'0','0',sg71);

dd23_2:k561ln1

port map(sg61,'0','0',sg74);

dd1_5_a:k561ln1

port map(sg63,'0','0',sg72);

dd1_5_b:k561ln1

port map(sg64,'0','0',sg73);

dd24:k514id2

port map(d(0)=>sg75,d(1)=>sg76,d(2)=>sg77,d(3)=>sg78,

q(0)=>sg79,q(1)=>sg80,q(2)=>sg81,q(3)=>sg82,

q(4)=>sg83,q(5)=>sg84,q(6)=>sg85);

p1<=sg67;

p2<=sg68;

p3<=sg69;

p4<=sg72;

p5<=sg73;

p6<=sg70;

k7<=sg89;

p8<=sg71;

zap<=sg74;

H<=sg60;

a<=sg79;

b<=sg80;

c<=sg81;

d<=sg82;

e<=sg83;

f<=sg84;

g<=sg85;

end shema;

Заключение.

В результате выполнения данной курсовой работы были изучены методы проектирования и разработки цифровых устройств в соответствии с данными технического задания. А также было изучено практическое применение ЭВМ для проектирования цифровых устройств. Для проектирования цифрового устройства был использован пакет языка описания Active-VHDL.

С использованием ЭВМ проектирование становится проще и эффективнее, а также мы можем изменить состав проекта или доработать уже существующий, и следовательно получить то, что нам нужно.

Библиографический список.

1. Шило В.Л.

«Популярные цифровые микросхемы»

Челябинск: Металлургия, 1989

2. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: в

2х томах. Том 1ый./Под ред. В.А. Шахнова./

М.: Радио и связь,1988

3. Схемотехника ЭВМ под ред. Г.Н. Соловьева.

М.: Высшая школа, 1985

Приложение:

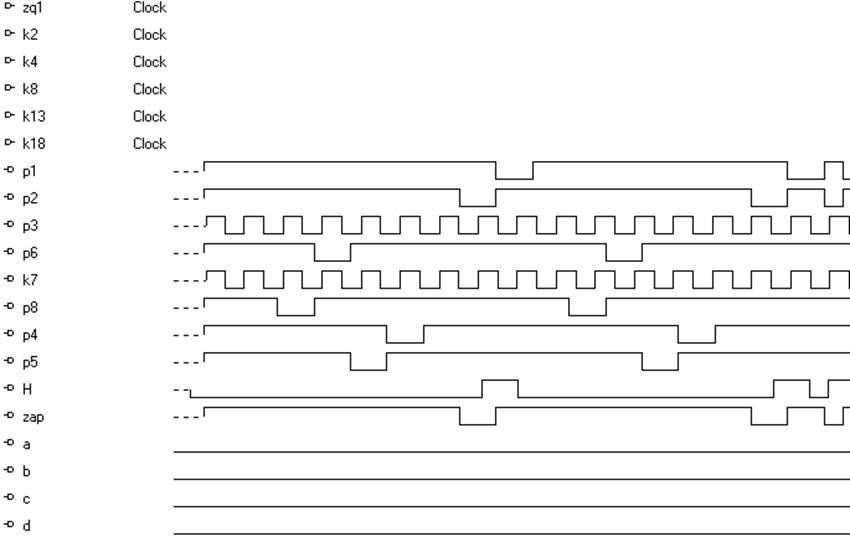

(Результаты работы схемы(Waveform))

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.