|

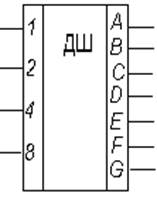

‘1’ |

‘2’ |

‘4’ |

‘8’ |

A |

B |

C |

D |

E |

F |

G |

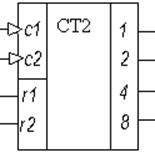

Условное обозначение

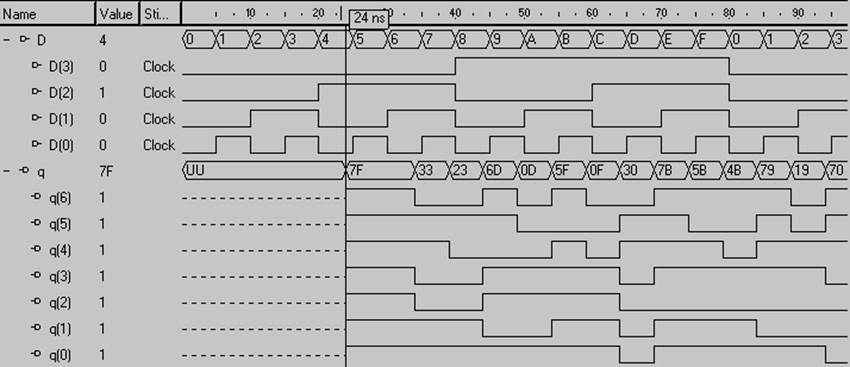

К514ИД2

Задержка - 24 нс

Таблица истинности элемента К514ИД2

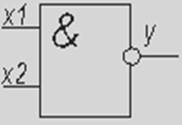

1.2 Микросхема К555ЛА3.

Данная микросхема представляет собой четыре логических элемента И-НЕ,

находящихся в одном корпусе. Содержит 64 интегральных элемента.

Данная микросхема представляет собой четыре логических элемента И-НЕ,

находящихся в одном корпусе. Содержит 64 интегральных элемента.

|

X1 |

X2 |

y |

|

1 |

1 |

0 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

0 |

0 |

1 |

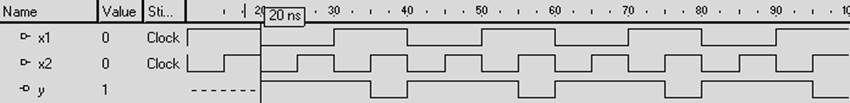

Условное обозначение

К555ЛА3

Задержка - 20 нс

Таблица истинности элемента К555ЛА3

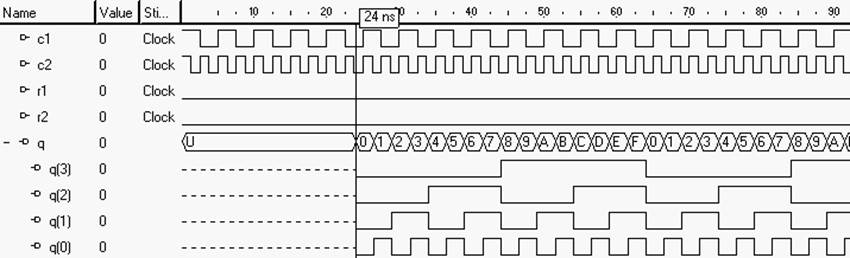

1.3 Микросхема К555ИЕ5.

Данная микросхема представляет собой двоичный счётчик, содержит 276 интегральных элементов.

Условное обозначение K555ИЕ5.

Задержка 24 нс.

|

r1 |

r2 |

‘1’ |

‘2’ |

‘4’ |

‘8’ |

|

1 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

Счёт |

|||

|

1 |

0 |

Счёт |

|||

|

0 |

0 |

Счёт |

|||

|

Счёт |

‘1’ |

‘2’ |

‘4’ |

‘8’ |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

|

2 |

0 |

1 |

0 |

0 |

|

3 |

1 |

1 |

0 |

0 |

|

4 |

0 |

0 |

1 |

0 |

|

5 |

1 |

0 |

1 |

0 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

0 |

|

8 |

0 |

0 |

0 |

1 |

|

9 |

1 |

0 |

0 |

1 |

|

10 |

0 |

1 |

0 |

1 |

|

11 |

1 |

1 |

0 |

1 |

|

12 |

0 |

0 |

1 |

1 |

|

13 |

1 |

0 |

1 |

1 |

|

14 |

0 |

1 |

1 |

1 |

|

15 |

1 |

1 |

1 |

1 |

Режим работы счётчика

К555ИЕ5

Последовательность счёта К555ИЕ5

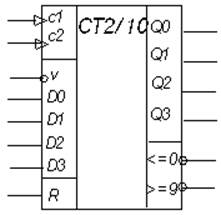

1.4 Микросхема К555ИЕ6.

Данная микросхема представляет собой двоично-десятичный счётчик, содержит 391 интегральный элемент.

Условное обозначение K555ИЕ6

Задержки: от С до ‘>=9’:24 нс.

от С до ‘<=0’:24 нс

|

R |

V |

C1 |

C2 |

D0 |

D1 |

D2 |

D3 |

Q0 |

Q1 |

Q2 |

Q3 |

P |

B |

|

1 |

‘X’ |

‘X’ |

0 |

‘X’ |

‘X’ |

‘X’ |

‘X’ |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

‘X’ |

‘X’ |

1 |

‘X’ |

‘X’ |

‘X’ |

‘X’ |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

‘X’ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

‘X’ |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

‘X’ |

1 |

‘X’ |

‘X’ |

1 |

Q(n):=D(n) |

0 |

1 |

|||

|

0 |

0 |

0 |

‘X’ |

1 |

‘X’ |

‘X’ |

1 |

Q(n):=D(n) |

1 |

1 |

|||

|

0 |

1 |

|

1 |

‘X’ |

‘X’ |

‘X’ |

‘X’ |

Счёт на увеличение |

1 |

1 |

|||

|

0 |

1 |

1 |

|

‘X’ |

‘X’ |

‘X’ |

‘X’ |

Счёт на уменьшение |

1 |

1 |

|||

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.