Санкт-Петербургский

Государственный Политехнический Университет

Санкт-Петербургский

Государственный Политехнический Университет

Факультет Технической Кибернетики

Кафедра Компьютерные Системы и Программные Технологии

ОТЧЕТ

о лабораторной работе №4.

Тема: Умножающие устройства.

|

Выполнил студент |

гр. 3081/2 Туркин Е.А |

|

Преподаватель |

Максименко С.Л. |

Санкт-Петербург

2010 г.

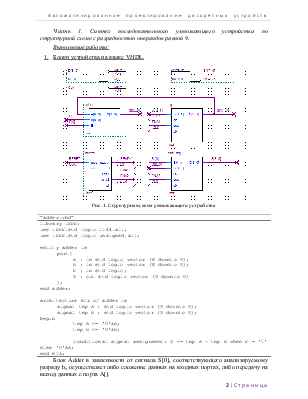

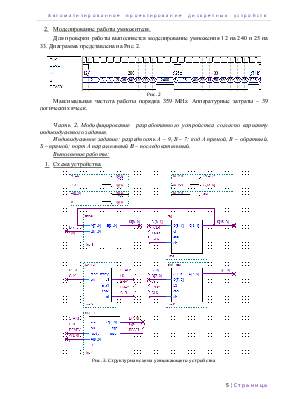

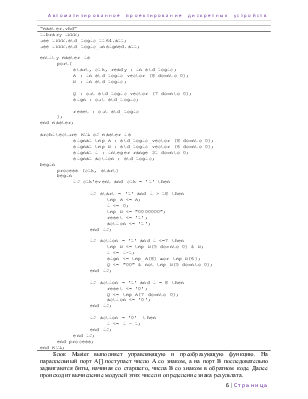

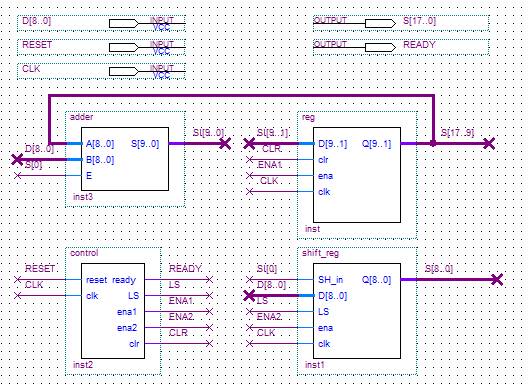

Часть 1. Синтез последовательного умножающего устройства по структурной схеме с разрядностью операндов равной 9.

Выполнение работы:

|

“adder.vhd” |

|

library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity adder is port( A : in std_logic_vector (8 downto 0); B : in std_logic_vector (8 downto 0); E : in std_logic; S : out std_logic_vector (9 downto 0) ); end adder; architecture RTL of adder is signal tmp_A : std_logic_vector (9 downto 0); signal tmp_B : std_logic_vector (9 downto 0); begin tmp_A <= '0'&A; tmp_B <= '0'&B; conditional_signal_assignment: S <= tmp_A + tmp_B when E = '1' else '0'&A; end RTL; |

Блок Adder в зависимости от сигнала S[0], соответствующего анализируемому разряду bi, осуществляет либо сложение данных на входных портах, либо передачу на выход данных с порта A[].

|

“reg.vhd” |

|

library IEEE; use IEEE.std_logic_1164.all; entity reg is port( D : in std_logic_vector (9 downto 1); Q : out std_logic_vector (9 downto 1); clr, ena, clk : in std_logic ); end reg; architecture RTL of reg is begin process (clk, clr, ena) begin if clr = '1' then Q <= (others => '0'); elsif ena = '0' then null; elsif clk'event and clk = '1' then Q <= D; end if; end process; end RTL; |

Блок Reg выполняет функцию регистра с асинхронным сбросом и разрешением работы.

|

“shift_reg.vhd” |

|

library IEEE; use IEEE.std_logic_1164.all; entity shift_reg is port( SH_in : in std_logic; D : in std_logic_vector (8 downto 0); LS, ena, clk : in std_logic; Q : out std_logic_vector (8 downto 0) ); end shift_reg; architecture RTL of shift_reg is signal sh_rg : std_logic_vector (8 downto 0); begin Q <= sh_rg; process (clk,ena) begin if clk'event and clk = '1' then if LS = '1' then sh_rg <= D; elsif ena = '1' then sh_rg <= SH_in & sh_rg(8 downto 1); end if; end if; end process; end RTL; |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.