Блок Master выполняет управляющую и преобразующую функцию. На параллельный порт А[] поступает число A со знаком, а на порт В последовательно задвигаются биты, начиная со старшего, числа В со знаком в обратном коде. Далее происходит вычисление модулей этих чисел и определение знака результата.

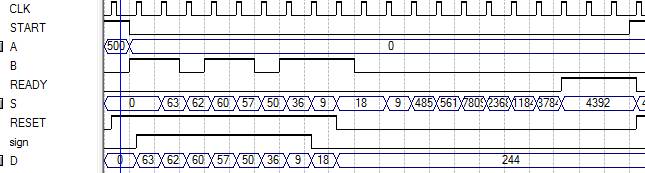

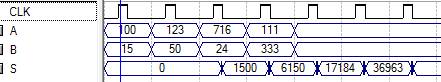

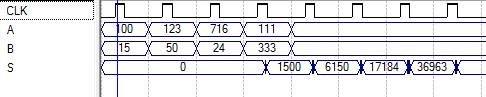

Для проверки работы выполняется моделирование умножения -244 на -18. Диаграмма представлена на Рис. 4.

Максимальная частота работы порядка 240 MHz. Аппаратурные затраты – 83 логические ячейки.

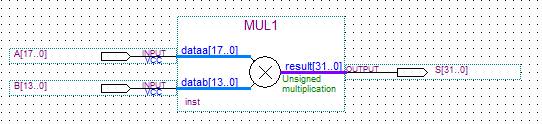

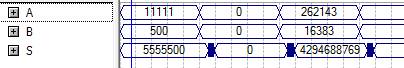

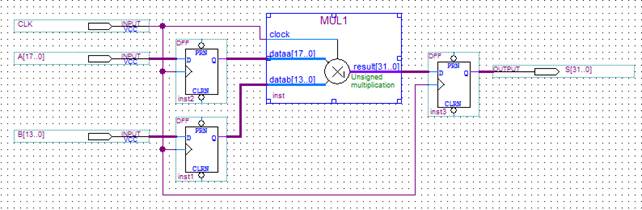

Часть 3. Исследование умножителя lpm_mult из состава библиотеки мегафункций.

Аппаратурные затраты - 330 логических ячеек.

Tpdmin = 17.866 ns

Tpdmax = 22.002 ns

После задания значения Tpd Requirement:

Tpdmin = 14.027 ns

Tpdmax = 15.324 ns

|

Аппаратурные затраты |

Tpdmin |

Tpdmax |

F max |

|

|

Неконвейеризированнный умножитель |

330 Logic Cells |

17.866 ns |

22.002 ns |

4.45 MHz |

|

Конвейеризированнный умножитель 1 ступень |

330 Logic Cells 178 Registers |

5.701 ns |

7.127 ns |

140.22 MHz |

|

Конвейеризированнный умножитель 2 ступени |

361 Logic Cells 291 Registers |

4.716 ns |

5.486 ns |

182.28 MHz |

|

Конвейеризированнный умножитель 3 ступени |

395 Logic Cells 323 Registers |

4.931 ns |

5.404 ns |

185.05 MHz |

|

Конвейеризированнный умножитель 4 ступени |

441 Logic Cells 437 Registers |

3.737 ns |

4.198 ns |

238.21 MHz |

|

Умножитель с использованием встроенных умножителей |

3.846 ns |

3.846 ns |

260.01 MHz |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.