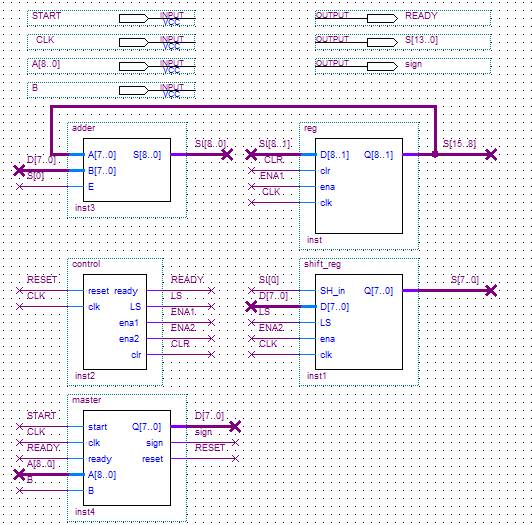

Блок Shift_Reg выполняет функцию сдвигающего регистра с синхронной загрузкой и разрешением сдвига.

|

“control.vhd” |

|

library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity control is port( reset, clk : in std_logic; ready, LS, ena1, ena2, clr : out std_logic ); end control; architecture RTL of control is signal i : integer range 15 downto 0; signal tmp_ready : std_logic; begin ready <= tmp_ready; process(clk,reset) begin if reset = '1' then clr <= '1'; LS <= '1'; ena1 <= '0'; ena2 <= '0'; tmp_ready <= '0'; i <= 0; else LS <= '0'; if clk'event and clk='1' and tmp_ready = '0' then clr <= '0'; ena1 <= '1'; ena2 <= '1'; tmp_ready <= '0'; if i = 9 then tmp_ready <= '1'; ena1 <= '0'; ena2 <= '0'; end if; i <= i+1; end if; end if; end process; end RTL; |

Блок Сontrol является управляющим устройством. При подаче сигнала RESET регистр reg устанавливается в 0, а в регистр shift_reg с шины D[N-1..0] загружается операнд В. После окончания начальной установки на шине D[N-1..0] устанавливается операнд А и начинается накопление произведения, которое завершается через N тактов. Когда произведение получено, устанавливается сигнал READY.

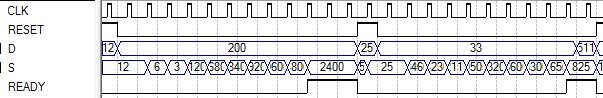

Для проверки работы выполняется моделирование умножения 12 на 240 и 25 на 33. Диаграмма представлена на Рис. 2.

Максимальная частота работы порядка 359 MHz. Аппаратурные затраты – 39 логических ячеек.

Часть 2. Модифицирование разработанного устройства согласно варианту индивидуального задания.

Индивидуальное задание: разрядность А – 9, В – 7; код А прямой, В – обратный, S – прямой; порт А параллельный B – последовательный.

Выполнение работы:

|

“master.vhd” |

|

library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity master is port( start, clk, ready : in std_logic; A : in std_logic_vector (8 downto 0); B : in std_logic; Q : out std_logic_vector (7 downto 0); sign : out std_logic; reset : out std_logic ); end master; architecture RTL of master is signal tmp_A : std_logic_vector (8 downto 0); signal tmp_B : std_logic_vector (6 downto 0); signal i : integer range 31 downto 0; signal action : std_logic; begin process (clk, start) begin if clk'event and clk = '1' then if start = '1' and i > 18 then tmp_A <= A; i <= 0; tmp_B <= "0000000"; reset <= '1'; action <= '1'; end if; if action = '1' and i <=7 then tmp_B <= tmp_B(5 downto 0) & B; i <= i+1; sign <= tmp_A(8) xor tmp_B(6); Q <= "00" & not tmp_B(5 downto 0); end if; if action = '1' and i = 8 then reset <= '0'; Q <= tmp_A(7 downto 0); action <= '0'; end if; if action = '0' then i <= i + 1; end if; end if; end process; end RTL; |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.