Санкт-Петербургский государственный политехнический университет

Факультет технической кибернетики

Кафедра автоматики и вычислительной техники

Отчет по лабораторной работе №5

(Учебная дисциплина «Автоматизации проектирования дискретных устройств»)

Работу выполнил студент группы №3081/2 Головченко Алексей

Работу принял преподаватель___________ Максименко С.Л.

Санкт-Петербург

2010

1. Исследование параметризованного модуля LPM_FIFO

С помощью мастера создадим FIFO на 64 8-разрядных слова.

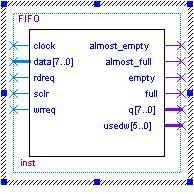

Данный FIFO имеет единый сигнал тактирования чтения и записи — вход clock, вход синхронного сброса — sclr, входы требования записи и чтения — wrreq и rdreq, вход данных, записываемых в FIFO — data[].

Выходные сигналы, характеризующие состояние FIFO:

- q[] - выходные данные;

- empty – показывает, что очередь пуста, запрещает чтение;

- full — показывает, что очередь заполнена, запрещает запись;

- usedw[] - количество слов в очереди;

- almost_empty — показывает, что очередь почти заполнена;

- almost_full — показывает, что очередь почти пуста.

Используемые аппаратные ресурсы СБИС ПЛ:

- 18 lut;

- 1 M4K – блок встроенной двухпортовой памяти;

- 22 reg;

Наименьшее значение максимальной тактовой частоты fmax — 287.44 MHz (period = 3.479 ns ).

Функциональное моделирование FIFO в различных режимах.

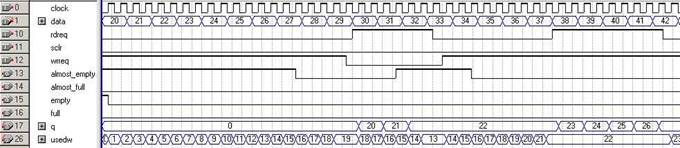

Моделирование при ADD_SHOWAHEAD = “OFF”. Временные диаграммы работы FIFO:

Рис. 1.1. Диаграмма работы FIFO.

При rdreq = 1 и фронте тактового импульса происходит запись в FIFO. До этого момента она пуста и выход empty установлен в 1. При записи usedw увеличивается на 1 при каждом новом тактовом импульсе, т.е. число слов в очереди увеличивается.

Пока wrreq = 0 на всех линиях выходной шины FIFO установлен 0. При wrreq = 1 и фронте тактового импульса происходит чтение слов из очереди, при этом usedw уменьшается на 1, при чтении слова покидают очередь.

При одновременном чтении и записи число слов в очереди остается постоянным, так как тактовый сигнал чтения и записи один и тот же.

Пока usedw < 16, то almost_empty = 1.

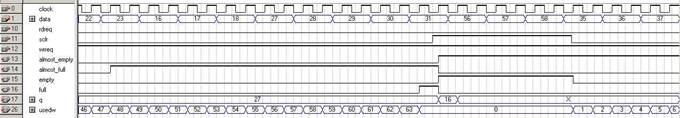

Рис. 1.2. Диаграмма работы FIFO.

При sclr = 1 происходит синхронный сброс очереди, она становится пустой (empty = 1), а на выходе получается не известно что.

Когда очередь полная full установлен в 1, usedw = 0, больше запись в очередь не происходит.

Когда sclr = 0, запись в очередь снова начинается.

Моделирование при ADD_SHOWAHEAD = “ON”. В этом случае на выходной шине очереди сразу появляются данные, даже если сигнал разрешения чтения не установлен.

Это показано на следующей временной диаграмме.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.