when q_H1 =>

TX_state <= q_N;

when q_N =>

if (DATA_len = 0) then

TX_state <= q_T1;

elsif (DATA_len /= 0) then

TX_state <= q_DATA;

end if;

when q_DATA =>

if (DATA_len /= 0) then

TX_state <= q_DATA;

elsif (DATA_len = 0) then

TX_state <= q_T1;

end if;

when q_T1 =>

if (timer = '1') then

TX_state <= q_T1;

elsif (timer = '0') then

TX_state <= q_H1;

end if;

end case;

if (timer <= '1') then

COUNT_2us <= (COUNT_2us + 1) mod 24;

else

COUNT_2us <= 0;

end if;

end if;

END PROCESS;

PROCESS (CLKtmp)

BEGIN

if rising_edge(CLKtmp) then

case TX_state is

when q_H1 =>

if (conv_integer(USEDW) = 0) then

timer <= '1';

DATA_len <= 0;

elsif (conv_integer(USEDW) < 8) then

DATA_len <= conv_integer(USEDW);

timer <= '1';

else

DATA_len <= 8;

timer <= '0';

end if;

when q_N =>

null;

when q_DATA =>

DATA_len <= DATA_len - 1;

when q_T1 =>

if (COUNT_2us = 23) then timer <= '0';

end if;

end case;

end if;

END PROCESS;

with TX_state select

DATA_out <=

"11111111" when q_H1,

conv_std_logic_vector(DATA_len,8) when q_N,

D_FIFO when q_DATA,

"10001111" when q_T1;

END TX_CONTROL_arch;

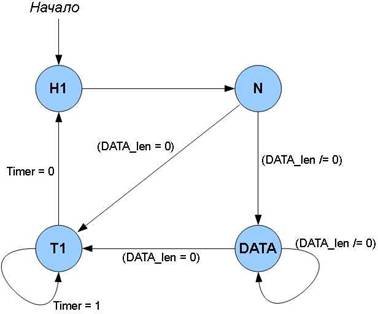

Блок TX_CONTROL работает по следующему алгоритму, который опишем конечным автоматом.

Формат передачи пакета:

Заголовок (Н1) — Число байт данных (N)— Данные (DATA) — Конец пакета (T1).

Если на момент передачи пакета данных нех, то передаем пустой пакет:

Заголовок — Число байт данных (00) Конец пакета.

Так как пакет состоит из 4х частей то у КА будет 4 состояния.

q_H1 – передача заголовка;

q_N — число передаваемых байт данных;

q_DATA — передача данных;

q_T1 — передача конца пакета;

Рис. 2.4.Алгоритм работы TX_CONTROL.

Конечный автомат синхронный. Из состояния q_H1 безусловный переход в состояние q_N, если есть данные, то происходит переход в состояние передачи данных, если нет, то переход в к передаче конца пакета. Если передается меньше чем заданное число данных, по причине того, что на момент передачи пакета их не хватает в очереди, передается что есть, и КА находится в состоянии q_T1 до того как обнулится таймер, отсчитывающий 2 мкс.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.