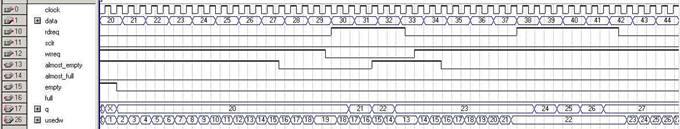

Рис. 1.3. Диаграмма работы FIFO.

Основные операционные узлы FIFO.

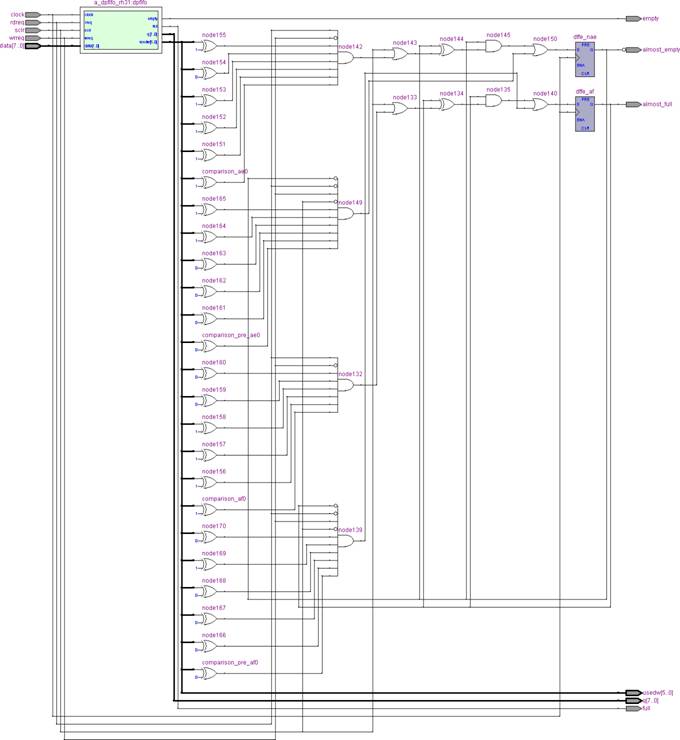

На верхнем уровне иерархии — SCFIFO – очередь с единым сигналом тактирования для чтения и для записи. Этот блок состоит из блока DPFIFO и логики для определения таких выходных состояний FIFO как almost_empty и almost_full.

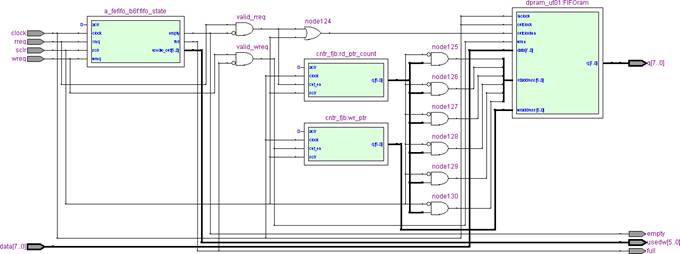

DPFIFO состоит из 4х блоков — блока памяти FIFOram в которой хранятся данные, двух счетчиков-указателей адреса записи в память и чтения из памяти и блока FIFO_STATE, выходные сигналы которого характеризуют состояние очереди — число элементов, пуста очередь или заполнена. С помощью этих сигналов и дополнительной логики происходит управление остальными 3мя блоками. Например, если очередь пуста, то запрещается чтение из памяти, это делается путем запрещения счета счетчика-указателя адреса записи памяти.

FIFOram представляет собой двухпортовую память и реализовано на ПЛИС с использованием 1го блока внутренней памяти.

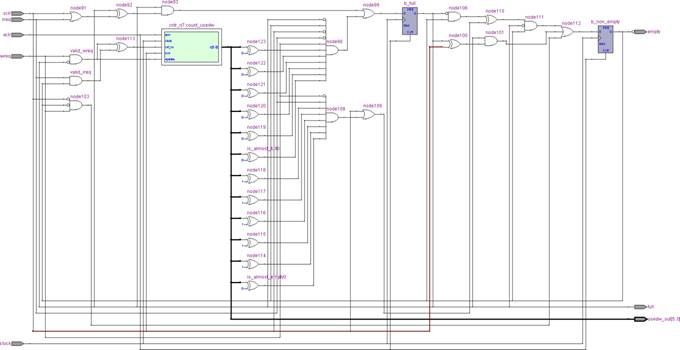

FIFO_STATE состоит из счетчика COUNT_USEDW, который фиксирует число слов находящихся в очереди и логики для определения пуста очередь или же наоборот заполнена.

Рис. 1.4. SCFIFO.

Рис. 1.5. DPFIFO.

Рис. 1.6. FIFO_STATE.

2. Устройство передачи данных с FIFO.

Задание:

|

Тип устройства |

Длина пакета |

Интервал |

Формат пакета |

LPM_SHOW-AHEAD |

Clk_out |

Clk_in |

|

|

4 |

Передатчик |

до 11 |

< 2us |

H1NdddT1 |

OFF |

CLK/2 |

CLK/4 |

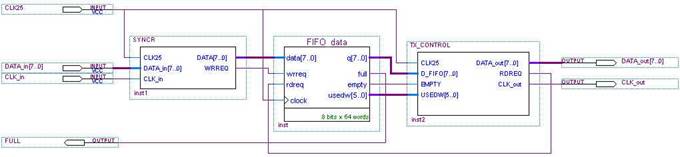

Устройство состоит из:

- Блока синхронизации входных данных SYNCR.

- Буферного FIFO.

- Передатчика TX_CONTROL формирующего пакеты с заданными характеристиками.

Рис. 2.1. Схема устройства

передачи данных с FIFO.

Листинг 1. SYNCR.vhd.

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY SYNCR is

port(

CLK25 : in std_logic;

DATA_in : in std_logic_vector (7 downto 0);

CLK_in : in std_logic;

DATA : out std_logic_vector (7 downto 0);

WRREQ : out std_logic

);

END SYNCR;

ARCHITECTURE SYNCR_arch of SYNCR is

signal DATA_tmp : std_logic_vector (7 downto 0);

signal WRREQ_tmp : std_logic;

BEGIN

DATA <= DATA_in;

WRREQ <= WRREQ_tmp;

PROCESS ( CLK_in,CLK25)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.