Санкт-Петербургский

Государственный Политехнический Университет

Санкт-Петербургский

Государственный Политехнический Университет

Факультет Технической Кибернетики

Кафедра Компьютерные Системы и Программные Технологии

ОТЧЕТ

о лабораторной работе №5.

Тема: Исследование FIFO.

|

Выполнил студент |

гр. 3081/2 Туркин Е.А |

|

Преподаватель |

Максименко С.Л. |

Санкт-Петербург

2010 г.

Часть 1. Исследование FIFO.

Исследование параметризируемого модуля LPM_FIFO из состава библиотеки мегафункций.

Исследование параметризируемого модуля LPM_FIFO из состава библиотеки мегафункций.fifo_s state – управляющее устройство, основная задача которого подсчёт числа байт в очереди и в зависимости от него формирование сигналов empty и full

FIFOram – память для хранения данных очереди. Обращение к памяти происходит по двум адресам – адрес для чтения и адрес для записи.

rd_ptr_count – счётчик адресов чтения.

wr_ptr – счётчик адресов записи.

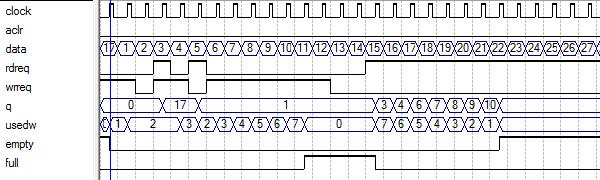

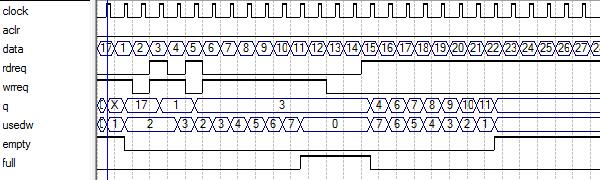

Основным отличием между диаграммами работы является появление данных на выходе на следующем такте после первого запроса на запись в режиме Showahead. Сигнал read_request, в данном случае, является сигналом для «смены данных на следующие».

В режиме Showahead при заполнении очереди сигнал empty остаётся до появления в очереди второго байта, т.к. первый байт сразу появляется на выходе.

Часть 2. Исследование устройства передачи данных с FIFO

|

“synchr.vhd” |

|

library IEEE; use IEEE.std_logic_1164.all; entity synchr is port( clk_25 : in std_logic; data_in : in std_logic_vector (7 downto 0); clk_in : in std_logic; data : out std_logic_vector (7 downto 0); wrreq : out std_logic ); end synchr; architecture RTL of synchr is begin process (clk_in, clk_25) variable tmp_clk : std_logic := '0'; begin if clk_25'event and clk_25 = '1' then if clk_in = '1' and tmp_clk = '0' then wrreq <= '1'; data <= data_in; tmp_clk := '1'; else wrreq <= '0'; end if; if clk_in = '0' then tmp_clk := '0'; end if; end if; end process; end RTL; |

Предающий блок формирует на выходе данные и сигнал запроса записи данных по первому фронту CLK_25 после фронта CLK_IN.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.