Двонаправлені канали А і В

по сигналах з систем керування СКА і СКВ

можуть виконувати наступні функції: запис інформації в регістри по каналу А,

запис по каналу В, одночасний запис по каналах А та В,

считування по каналу А, считування по каналу В, одночасне

считування по каналах А та В, запис по каналу А та

считування по каналу В та навпаки. При відсутності сигналу дозволу

обміну по каналу ![]() =

1 виходи відповідного каналу находяться в високоомному стані. Сигнали керування

– потенційні.

=

1 виходи відповідного каналу находяться в високоомному стані. Сигнали керування

– потенційні.

Своєрідне використання находить

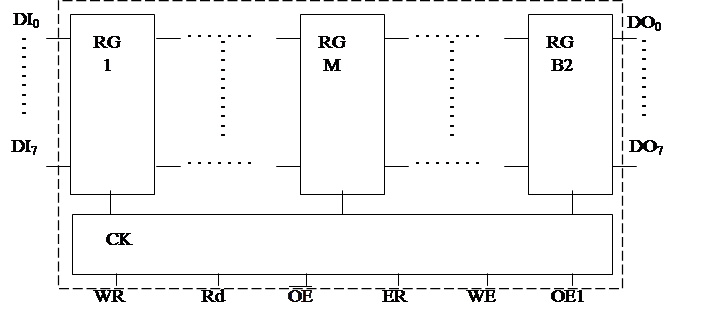

регістр пам’яті магазинного типу, ємністю 32![]() 8 біт

(мікросхема К1002КР1). В цій мікросхемі регістри з’єднані у відповідності до схеми, приведеної

ни рис.6.17.

8 біт

(мікросхема К1002КР1). В цій мікросхемі регістри з’єднані у відповідності до схеми, приведеної

ни рис.6.17.

|

Рис.6.17

Головним керуючим елементом мікросхеми є система керування СК, яка вирішує питання переміщення інформації з одного регістра в інший цілим словом. Операція запису по входах DI0 – DI7 виконується при WR= 1. Вихід WE (write enable) видає сигнал готовності мікросхеми до прийняття для захисту наступного байта інформації. При появі WR = 1 сигнал WE переводиться в нуль, і коли інформація переміститься в лругий регістр, на виході WE = 1. При повному заповненні ЗП на виході WE = 0.

Зчитуваня інформації виконується

послідовно в часі з виводівDO при сигналі дозволу виходу ![]() = 0 (output enable) і по сигналу RD = 1.Сигнал на виході ОЕ1 = 1

інформує про готовність мікросхеми до зчитування наступного байта. При появі

чергового сигналу зчитування вихід ОЕ1 переходить в нульовий стан і при

переміщенні інформації з передостаннього регістра в останній на виході ОЕ1

появляється “1”. При відсутності інформації в ЗП ОЕ1 = 0.

= 0 (output enable) і по сигналу RD = 1.Сигнал на виході ОЕ1 = 1

інформує про готовність мікросхеми до зчитування наступного байта. При появі

чергового сигналу зчитування вихід ОЕ1 переходить в нульовий стан і при

переміщенні інформації з передостаннього регістра в останній на виході ОЕ1

появляється “1”. При відсутності інформації в ЗП ОЕ1 = 0.

При подачі сигналу ОЕ = 1 (“блокування”) виходи даних DO0 – DO7 і ОЕ1 переходять в третій стан, вхід RD блокується і можливий лиш запис інформації.

З приведеного аналізу видно, що особливість ЗП магазинного типу полягає в тому, що він не допускає довільну виборку елемента пам’яті або слова. Але в цій структурі є можливість організації запису – зчитування інформації через одні й ті ж входи/виходи. В такому випадку записане в ЗП інформація буде считуватись в зворотньому порядку. Такі ЗП називають “стек”.

Регістрові ЗП магазинного типу використовуються в тих випадках, коли необхідно узгодити роботу пристроїв з різними швидкостями передачі інформації, працюючими в асинхронних режимах.

|

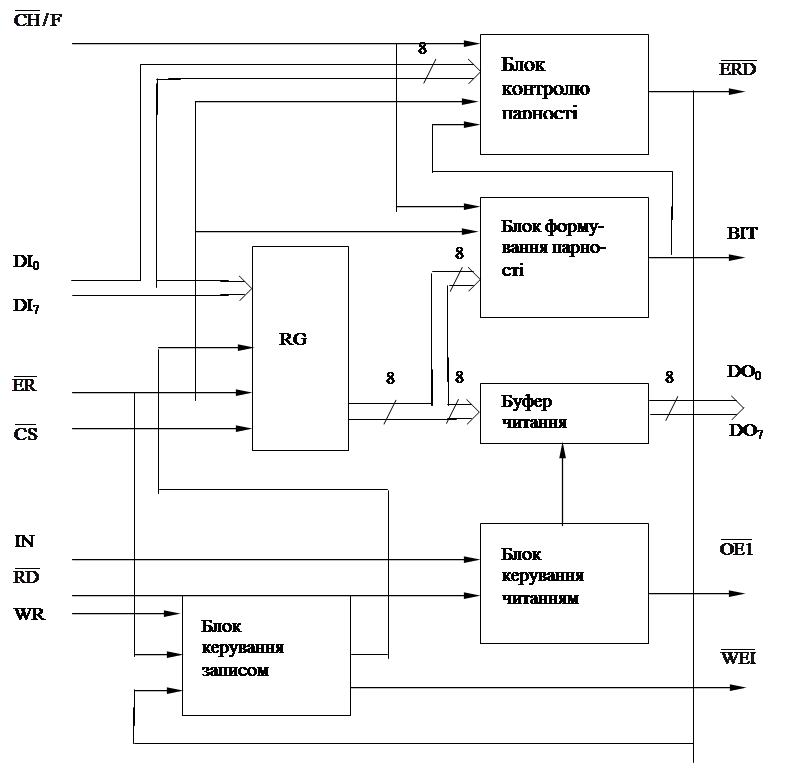

Рис.6.18

Не менш важливе значення для практики використання регістрових схем пам’яті мають мікросхеми багаторежимних буферних регістрів ББР, які призначені для побудови інтерфейсних блоків, контролерів зовнішніх пристроїв, закінчених блоків ЗП. (Рис.6.18)

Головний

функціональний пристрій приведеної схеми є регістр RG, інформація в який записується по входах DI при наявності сигналів ![]() = 0 і

= 0 і ![]() = 0. Считування

інформації виконується по сигналу

= 0. Считування

інформації виконується по сигналу ![]() = 0,

= 0, ![]() = 0 через вихідний

буфер читання і виходи DO.

При необхідності вихідний код сигналом IN інвертується. Якщо

= 0 через вихідний

буфер читання і виходи DO.

При необхідності вихідний код сигналом IN інвертується. Якщо ![]() =

1,то мікросхема находиться в третьому стані.

=

1,то мікросхема находиться в третьому стані.

Однією з найважливіших характеристик

мікросхеми є контроль парності одиниць в інформаційному слові, що записується в

регістр або зчитується з нього. Робота блоку контроля парності поєднана з

роботою блока формування біта парності. Останній блок контролює парність

одиниць в приймаємому сигналі. Якщо число одиниць парне, то вихід ВІТ =

0, якщо непарне, то ВІТ = 1. В такому випадку дев’ятирозрядний сигнал ВІТ

+ DO буде завжди мати

парну кількість одиниць. Це дозволяє аналогічній мікросхемі прийняти сигнал по

входу DI і з допомогою

блоку контролю парності проконтролювати парність одиниць. Якщо умова парності

не виконується на виході ![]() формує сигнал

похибки, що блокує запис інформації в регістр. Сигнал

формує сигнал

похибки, що блокує запис інформації в регістр. Сигнал ![]() визначає

режим контролю на парність (при 0), або режим формування біта парності (при 1).

Такі режими важливі при роботі регістра з модулями ОЗП для захисту модуля від

хибної інформації.

визначає

режим контролю на парність (при 0), або режим формування біта парності (при 1).

Такі режими важливі при роботі регістра з модулями ОЗП для захисту модуля від

хибної інформації.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.