|

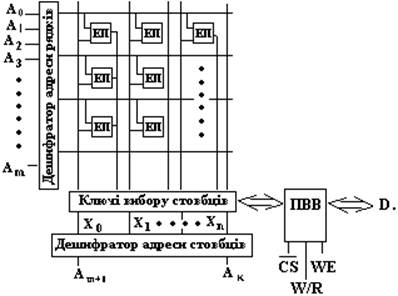

Рис.6.1

.

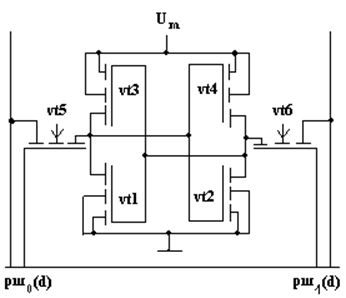

На рис.6.2 приводиться варіант побудови елементу пам’яті на польових транзисторах доповнюючого типу.

Транзистори VТ1,VТ2 виконані з каналами n-типу, а VT3,VT4-з каналами p-типу. Подібними ключами наVT5,VT6 виходи-входи тригера з’єднані з розрядними шинами РШ0 та РШ1 , по яких інформація підво- диться до тригера при записі інформації, та відводиться при читанні. При xі=1 транзистори VT5, VT6 відкриваються і підключають входи-виходи тригера до розрядних шин. При xі=0 транзистори VT5, VT6 закриваються і ізолюють тригер пам’яті від розрядних шин. Стан тригера, при якому при відкритому VT6 та VT5 вихід РШ1(d)=1, а РШ0(d)=0 являється станом збереження логічної 1. При РШ1(d)=0 в елементі пам’яті зберігається 0. При читанні інформації з ЕП-шини РШ1(d), та РШ0(d) являються ізольо- ваними від загальної шини, а тому передають інформацію через відповідні ключі вибору стовбців та ПВВ на зовнішню шину даних do, тобто (data out).

Для звернення до мікросхеми для запису 1 або 0 необхідно підвести цю інформацію до входу di(data in), подати необхідний код адреси

А(А0…Ак),

дозволяючий сигнал вибору мікросхеми CS(chip select), відповідний сигнал на вхід запису - читання W/R(write/read) та дозвіл  запису (WE). При вказаних сигналах з’являється сигнал xі=1

і відкривається доступ до всіх ЕП і-го рядка, водночас з’являється 1 на Yj стовбці

запису (WE). При вказаних сигналах з’являється сигнал xі=1

і відкривається доступ до всіх ЕП і-го рядка, водночас з’являється 1 на Yj стовбці

дешифратора стовбців, відкриваються відповідні транзисторні ключі дешифратора

Рис.6.2

стовбців.

Доступ до елементів пам’яті забезпечується при CS=1, а запис інформації в ЕП –при W/R=1. Читання забезпечується при W/R=0.

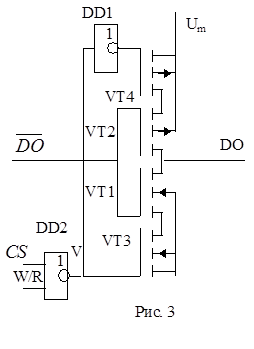

Мікросхеми пам’яті забезпечуються вихідним ключовим підсилюва- чем, що забезпечує два стани – високоомний та режим передачі сигналу з інвертуванням. Схема подібного інвертора приведена на мал.3.

На VТ1 та VT2 виготовлений інвертор, який доповнений транзис- торними ключами на VT3 та VT4, що керуються сигналом V. При V=0, VT3 та VT4 закриті і вихід знаходиться у високомному стані. При V=1 ключі на VT3, VT4 відкриті, і інвертор буде передавати нформацію. Сигнал V формується елементом DD2 в відповідності до логічної функції:

![]()

![]() V=CS+W/R

V=CS+W/R

Наявність такого виходу в мікросхемах пам’яті дозволяє з’єднувати інфор- маційні входи та виходи для підключення їх до єдиної шини даних.

По аналогії з іншими цифровими пристроями для освітлення режимів роботи ОЗП використовуються таблиці станів. В табл.6.1 приводиться, як приклад, таблиця станів мікросхеми статичного ОЗП.

Табл. 6.1.

|

|

W/R |

A5A7 |

DI |

DO |

Режим роботи |

|

1 |

Х |

Х |

Х |

Z |

збереження |

|

0 |

1 |

А |

0 |

Z |

Запис 0 |

|

0 |

1 |

А |

1 |

Z |

Запис 1 |

|

0 |

0 |

А |

Х |

|

Зчитування |

|

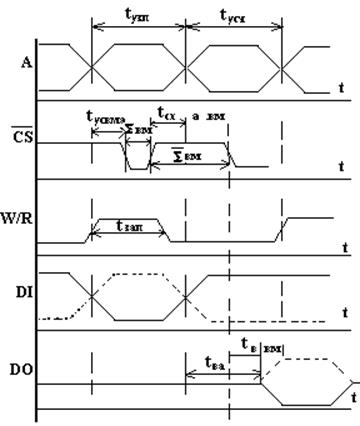

Рис.6.4

На рис.6.4 приведені діаграми, які відображають необхідні часові співвід- ношення між сигналами, що взаємно діють на входах та виходах мікрос- хеми пам’яті і необхідні для забезпечення безпомилкового запису та зчитування даних. Адресні сигнали А характеризуються часовими інтерва- лами tц зп , tц зч - час циклу запису інформації, та час циклу зчитування. Одночасно з адресними сигналами на вхід мікросхеми подаються і сигнали для запису інформації в мікросхему DI. Вхідний сигнал W/Rможе подава- тись водночас з адресними сигналами, та інформаційними DI, або з затримкою, необхідною для встановлення перехідних процесів після подання попередніх сигналів. Тривалість запису tзат цього сигналу повинна перевищувати суму часу tвс вм а – (час встановлення перехідних процесів після подання попередніх сигналів (наприклад, адресних)), та часу вибору інформації(tвм -час вибору мікросхеми ), тобто

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.