Y2<=(x4 and not x1) or (not x4 and not x3 and not x2)

|

Y3 |

x2x1 |

||||

|

x4x3 |

00 |

01 |

11 |

10 |

|

|

00 |

X |

0 |

1 |

1 |

|

|

01 |

X |

0 |

0 |

0 |

|

|

11 |

0 |

0 |

0 |

X |

|

|

10 |

1 |

X |

0 |

1 |

|

Y3<=(x4 and not x3 and not x1) or (not x4 and not x3 and x2)

Текст VHDL – описания данной системы представлен ниже

Library ieee;

Use ieee.std_logic_1164.all;

Entity KS is

Port(x4,x3,x2,x1:in std_logic;

Y1,y2,y3: out std_logic);

End KS;

Architecture KS of KS is

Begin

Y1<=(not x3 and not x2) or (not x3 and x1) or (x4 and x3 and not x1);

Y2<=(x4 and not x1) or (not x4 and not x3 and not x2);

Y3<=(x4 and not x3 and not x1) or (not x4 and not x3 and x2);

End KS;

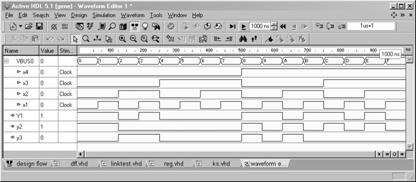

Временные диаграммы функционирования системы приведены на рисунке.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.