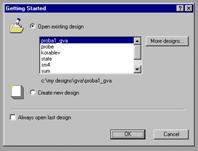

После запуска системы в диалоговом окне выбрать Create new design.

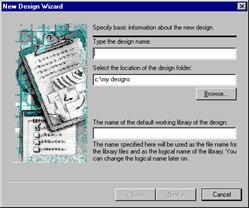

Вторым шагом создания проекта - ввести имя проекта и его расположение. В качестве папки проектов выбирать c:\users\vhdl. Выбираем Create new source files.

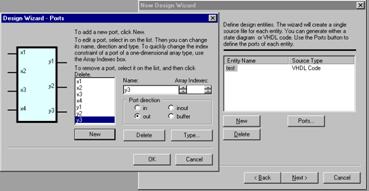

Третьим шагом задаем имя entity и описываем порты.

В результате формируется исходный текст на языке VHDL, содержащий

объявление entity и архитектурного тела. Структура проекта отображается в

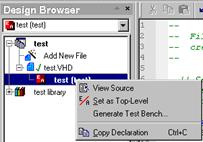

менеджере проекта Design Browser

После ввода описания проекта исходные файлы компилируются, и в менеджере проекта в исходном файле появляется entity и architecture. В случае наличия ошибок в исходном тексте компилятор выдает список с указанием положения и характера. После успешной компиляции необходимо entity проекта установить как Set as top level, выбрав данный пункт из контекстного меню.

Верификация проекта осуществляется подачей счетчиковой

последовательности на входы компонента. Для этого необходимо создать временную

диаграмму (кнопка ![]() ).

Из контекстного меню выбрать Добавить сигналы.

).

Из контекстного меню выбрать Добавить сигналы.

![]()

Для создания счетчиковой последовательности необходимо на входы испытываемой схемы подать сигналы с удваивающейся частотой. Это реализуется с помощью добавления стимуляторов. Стимулятор можно добавить двойным щелчком на сигнале, или выбрать пункт Stimulators... из контекстного меню. Для каждого сигнала установить вид стимулятора Clock и ввести частоту. Обычно в качестве набора частот используется 1МГц, 2МГц, 4МГц, 8МГц, 16МГц, и т.д.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.