Задание 3. Построить структурную модель управляющего автомата из задания 2 на базе триггера, синтезированного в задании 1.

Пример выполнения лабораторной работы

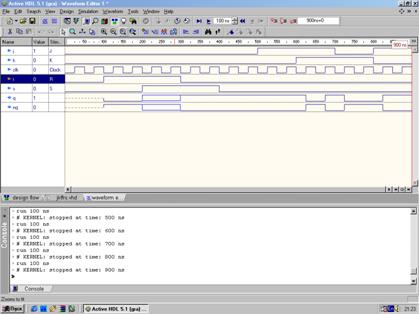

Задание 1. Построить модель синхронного JK –

триггера со входами асинхронного сброса и установки. Условное графическое

обозначение проектируемого компонента приведено на рисунке.

Задание 1. Построить модель синхронного JK –

триггера со входами асинхронного сброса и установки. Условное графическое

обозначение проектируемого компонента приведено на рисунке.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity jkffrs is

generic(

Tclk,Tclr,Tsu:Time:=0ns

);

port(

j : in STD_LOGIC;

k : in STD_LOGIC;

clk : in STD_LOGIC;

s : in STD_LOGIC;

r : in STD_LOGIC;

q : out STD_LOGIC;

nq : out STD_LOGIC

);

end jkffrs;

--}} End of automatically maintained section

architecture jkffrs of jkffrs is

signal qt:std_logic;

begin

-- enter your statements here --

process(clk,s,r) is

subtype slv2 is std_logic_vector(1 downto 0);

begin

case slv2'(r&s) is

when "11"=>qt<='X' after (Tsu+Tclr)/2;

when "10"=>qt<='0' after Tclr;

when "01"=>qt<='1' after Tsu;

when "00"=>if rising_edge(clk) then

case slv2'(j&k) is

when "01"=>qt<='0' after Tclk;

when "10"=>qt<='1' after Tclk;

when "11"=>qt<=not qt after Tclk;

when others=>null;

end case;

end if;

when others=>null;

end case;

end process;

q<=qt;

nq<=not qt;

end jkffrs;

Задание 2. Построение модели управляющего автомата.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.