(см. табл. 6.18). Контроль

самодвойственности функции ![]() состоит в проверке в

каждом периоде того факта, что значения функции в информационном и контрольном

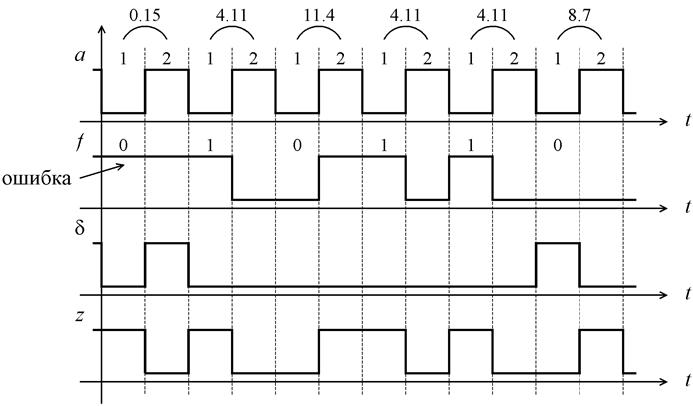

тактах инверсны друг другу. На рис. 6.54 приведена временная диаграмма работы

схемы при наличии в ней неисправности «константа 0» на нижнем входе элемента 2.

состоит в проверке в

каждом периоде того факта, что значения функции в информационном и контрольном

тактах инверсны друг другу. На рис. 6.54 приведена временная диаграмма работы

схемы при наличии в ней неисправности «константа 0» на нижнем входе элемента 2.

Рис.6.54. Временная диаграмма работы схемы с неисправностью

Эта неисправность проявляется на

наборах 7 и 15 путем искажения значения сигнала ![]() типа 0

типа 0 ![]() 1. Поэтому у сигнала z нарушается

самодвойственность в первом и последнем периодах временной диаграммы, когда на

вход поступают наборы 0, 15 и 8, 7.

1. Поэтому у сигнала z нарушается

самодвойственность в первом и последнем периодах временной диаграммы, когда на

вход поступают наборы 0, 15 и 8, 7.

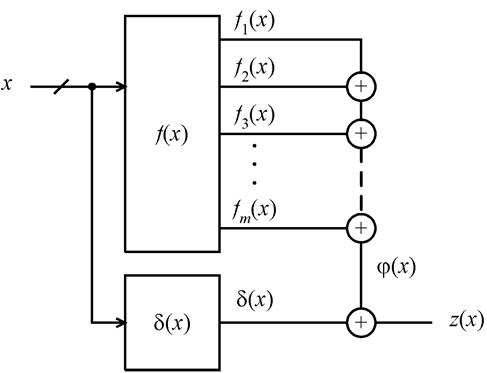

На рис. 6.55 приведена схема контроля на основе самодвойственного паритета.

Рис.6.55. Схема самодвойственного паритета

В этом случае выходы основного

блока ![]() объединяются с помощью схемы из элементов

М2 для расчета бита четности

объединяются с помощью схемы из элементов

М2 для расчета бита четности ![]() . Блок

. Блок ![]() реализует

реализует ![]() -функцию,

дополняющую

-функцию,

дополняющую ![]() до самодвойственной функции

до самодвойственной функции ![]() .

.

6.8. Обнаружение неисправностей в схемах с памятью

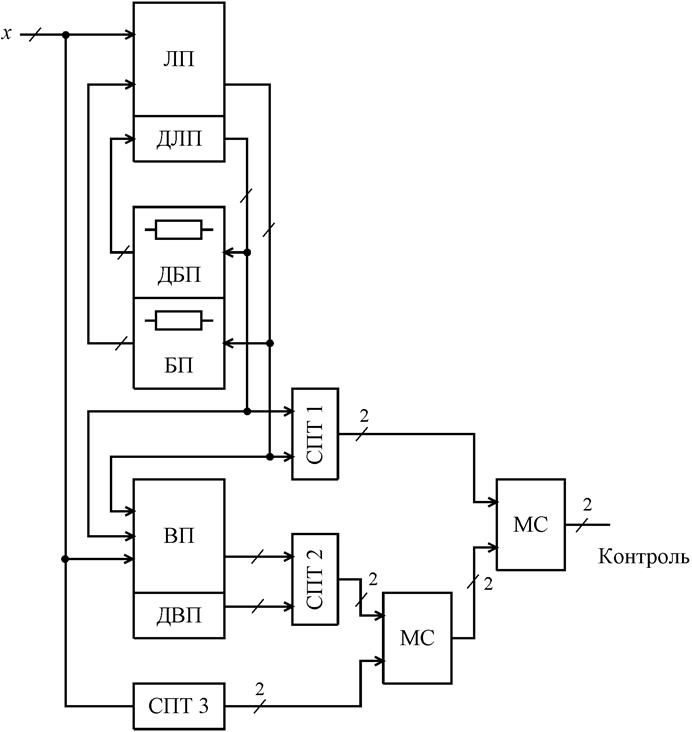

На рис. 6.56 приведена структура многотактной схемы с обнаружением отказов.

Рис.6.56. Структура многотактной схемы с обнаружением отказов

Комбинационная часть схемы разделена на два блока. Логический преобразователь (ЛП) реализует функции включения элементов памяти (ЭП), составляющих блок памяти (БП), а выходной преобразователь (ВП) – функции выходов.

Для организации

контроля в схему вводятся дополнительные ЭП (блок ДБП) с таким расчетом, чтобы

векторы ![]() , соответствующие рабочим внутренним

состояниям схемы, являлись словами какого-либо кода с обнаружением ошибок. При

этом разряды вектора

, соответствующие рабочим внутренним

состояниям схемы, являлись словами какого-либо кода с обнаружением ошибок. При

этом разряды вектора ![]() соответствуют основным ЭП,

расположенным в блоке БП, а разряды

соответствуют основным ЭП,

расположенным в блоке БП, а разряды ![]() – дополнительным ЭП,

расположенным в блоке ДБП. Для управления дополнительными ЭП формируется дополнительный

логический преобразователь (блок ДЛП). Для контроля ВП используется другой код

с обнаружением ошибок. При этом могут вводиться дополнительные контрольные

выходы схемы, реализуемые дополнительным выходным преобразователем (блок ДВП).

– дополнительным ЭП,

расположенным в блоке ДБП. Для управления дополнительными ЭП формируется дополнительный

логический преобразователь (блок ДЛП). Для контроля ВП используется другой код

с обнаружением ошибок. При этом могут вводиться дополнительные контрольные

выходы схемы, реализуемые дополнительным выходным преобразователем (блок ДВП).

Неисправности элементов

блоков ЛП и БП приводят к искажению вектора ![]()

![]() , характеризующего состояние системы

элементов памяти, что фиксируется самопроверяемым тестером СПТ1. Тестер СПТ2

контролирует исправное состояние блоков ВП и ДВП. Если на вход схемы информация

поступает также в виде слов кода с обнаружением ошибок, то последний

контролируется при помощи СПТ3. Парафазные выходы всех тестеров объединяются посредством

МС, в результате чего образуется единый парафазный выход контроля.

, характеризующего состояние системы

элементов памяти, что фиксируется самопроверяемым тестером СПТ1. Тестер СПТ2

контролирует исправное состояние блоков ВП и ДВП. Если на вход схемы информация

поступает также в виде слов кода с обнаружением ошибок, то последний

контролируется при помощи СПТ3. Парафазные выходы всех тестеров объединяются посредством

МС, в результате чего образуется единый парафазный выход контроля.

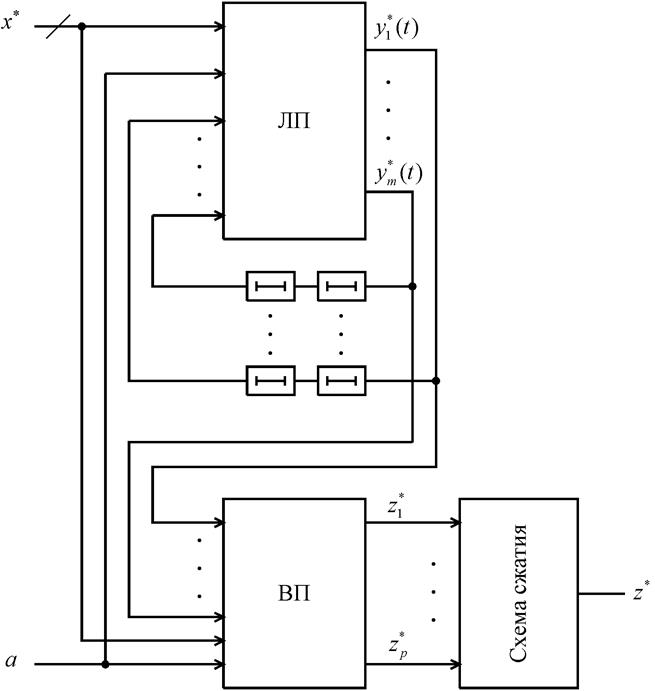

На рис. 6.57 приведена структура самопроверяемой самодвойственной многотактной схемы.

Рис.6.57. Структура самопроверяемой самодвойственной

многотактной схемы

Логический и выходной

преобразователи, являющиеся комбинационными схемами, преобразуются в

самодвойственные схемы в соответствии с рис. 6.46. В образованной схеме ЛП

описывается СД-функциями ![]() , а ВП – самодвойственными

функциями

, а ВП – самодвойственными

функциями ![]() . Линии задержки (ЛЗ) дублируются. Каждая

ЛЗ осуществляет задержку на время, равное половине периода импульсной

последовательности

. Линии задержки (ЛЗ) дублируются. Каждая

ЛЗ осуществляет задержку на время, равное половине периода импульсной

последовательности ![]() (см. рис. 6.40).

Самодвойственные сигналы, формируемые на выходах блока ВП, при помощи схемы

сжатия сводятся к одному контрольному сигналу

(см. рис. 6.40).

Самодвойственные сигналы, формируемые на выходах блока ВП, при помощи схемы

сжатия сводятся к одному контрольному сигналу ![]() .

Неисправности элементов ЛП и линий задержки приводят к появлению несамодвойственных

сигналов на входах ВП, что фиксируется по выходу

.

Неисправности элементов ЛП и линий задержки приводят к появлению несамодвойственных

сигналов на входах ВП, что фиксируется по выходу ![]() .

.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.