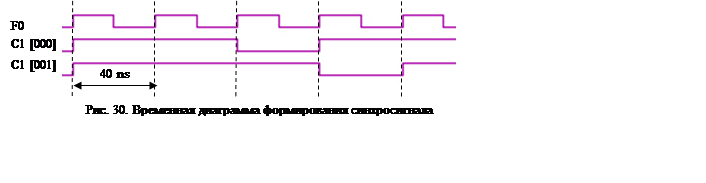

будут использоваться всего 2-а значения кода, при RGMK[Tцикла] = 000 à Тцикла = 120 нс, при RGMK[Tцикла] = 001 à Тцикла = 160 нс. Конечно, это упрощает кодирование МК, но при принятом кодировании МК остаётся невостребованным старший бит поля Tцикла .

|

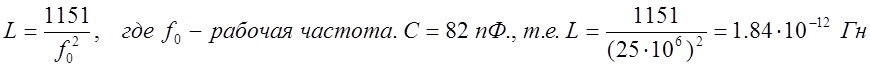

При использовании кварцевого резонатора с частотой более 20 МГц, в цепь входа FC1, ИМС К1804ГГ1, необходимо включить параллельный колебательный контур, между конденсатором (с C >1000 пФ) и землей, чтобы предотвратить возбуждение генератора на первой гармонике [4].

Параметры элементов входящих в данный контур

рассчитываются следующим образом:

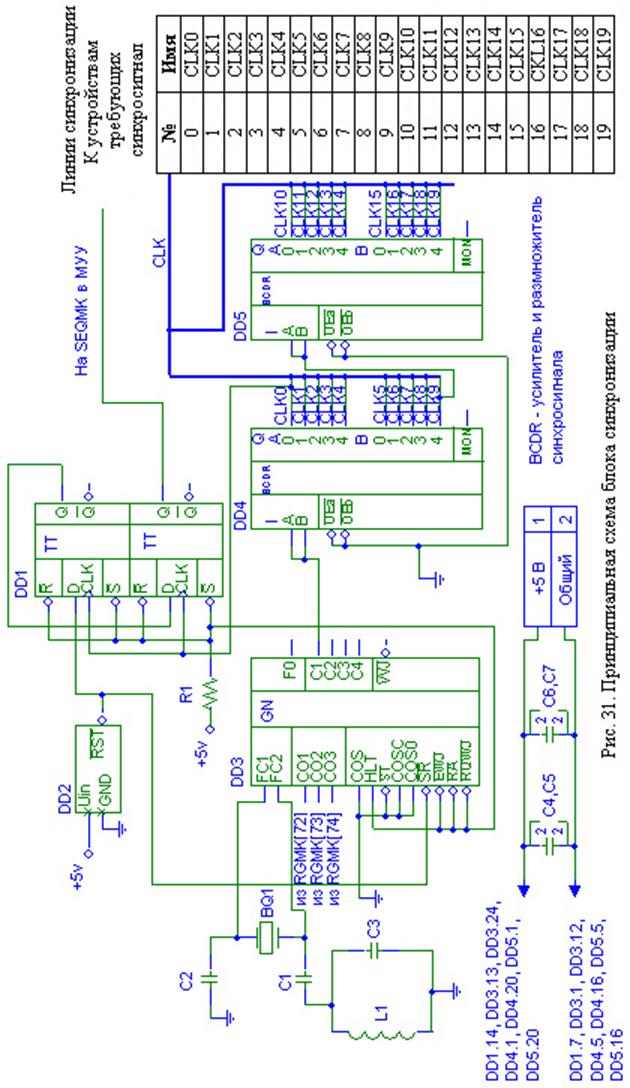

8.4 Принципиальная схема блока синхронизации

|

Поз. обозна-чение |

Наименование |

Кол |

Примечание |

|

BQ1 |

25 МГц |

1 |

|

|

C1 |

Конденсатор КМ5Б – Н30 – 16 |

1 |

|

|

C2 |

Конденсатор КМ5Б – Н30 – 68 |

1 |

|

|

C3 |

Конденсатор КМ5Б – Н30 – 1100 |

1 |

|

|

С4 |

Конденсатор КМ5Б – Н30 – 82 |

1 |

|

|

DD1 |

КР1554ТМ2 |

1 |

|

|

DD2 |

MC34064 |

1 |

|

|

DD3 |

К1804ГГ1 |

1 |

|

|

DD4, DD5 |

IDT49FCT805CT |

2 |

|

|

L1 |

2 пГ |

1 |

|

|

R1 |

МЛТ – 2 - 10 КОм ± 10 % |

1 |

|

|

Табл. 1. Перечень элементов принципиальной схемы блока синхронизации |

|||

|

Номер бита |

Наименование поля |

Функциональное описание |

|

Операционный блок |

||

|

ЦПЭ (4*К1804ВС1 + К1804ВР1) |

||

|

0 |

SEL |

Выбор источника адресов РОНA,B (L-RGK, H-RGMK) |

|

1…4 |

A |

Адрес чтения/записи РЗУ А |

|

5…8 |

B |

Адрес чтения/записи РЗУ B |

|

9…17 |

IOB |

Микроинструкции для ОБ |

|

MUXC, логика сдвигов, SRG, MUXTST (К1804ВР2) |

||

|

18…30 |

IВС2 |

Микроинструкции БИС К1804ВР2 |

|

31 |

|

Вход разрешения записи словосостояния в регистры состояния программ и МКпрограмм |

|

32 |

|

Вход разрешения выполнения сдвигов |

|

33 |

|

Вход разрешения вывода словосостояния из SRG на LDB ОБ |

|

Входные и выходные регистры ( RGDin, RGDout, RGA) |

||

|

34 |

|

Разрешение вывода данных из RGDin на LDB ОБ |

|

35 |

|

Бит разрешения загрузки данных в RGDin с DB |

|

36 |

|

Разрешение вывода данных из RGDоut на DB |

|

37 |

|

Бит разрешения загрузки данных в RGDin с Y ОБ |

|

38 |

|

Разрешение вывода данных из RGA на AB |

|

39 |

|

Бит разрешения загрузки данных в RGA с Y ОБ |

|

Параллельный умножитель (IDT7217L16) |

||

|

40 |

|

Бит разрешения загрузки регистрa входных данных RGX |

|

41 |

|

Бит разрешения загрузки регистрa входных данных RGY |

|

42 |

|

Бит управления селекторным входом для выбора данных, выводимых через порт Р. MSPSEL=L вывод в порт Р старшей части слова (результата произведения) из регистра старшей части произведения , а MSPSEL=H младшей части слова из регистра младшей части произведения |

|

43 |

|

Бит управления разрешением вывода результата произведения в порт Р |

|

44 |

XmYm |

Реализация знакового умножения. |

|

45 |

RND |

Округление результата |

|

46 |

|

Бит разрешения загрузки регистра произведения |

|

Поле const |

||

|

47 |

|

Поле разрешения вывода CONST на LDB ОБ |

|

48…63 |

CONST |

CONST подающаяся на LDB ОБ |

|

Микропрограммное устройство управления |

||

|

64 |

|

Разрешение условного перехода |

|

65 |

CCPOL |

Управление полярностью кода условия |

|

66 |

|

Запись в RGA/Счётчик SEQMK |

|

67 |

Co |

Приращение счетчика команд в SEQMK на 1 при Co = H |

|

68…71 |

Iseq |

Инструкции SEQMK |

|

Блок синхронизации |

||

|

72…74 |

Tцикла |

Поле управления длительностью цикла |

|

Основная память |

||

|

75 |

|

Разрешение записи в SRAM модуль |

|

76 |

|

Разрешение работы с памятью |

|

77 |

|

Разрешение вывода данных на DB из ОП |

|

78, 79 |

RESERV |

Не занятые биты в МК (при программировании МПП должны быть равными 0) |

|

МУУ |

||

|

80…91 |

АП |

Адрес перехода |

|

Табл.2 Формат микроинструкций (МК) |

||

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.