Каждая «линия ошибки» должна идти к какому-то индикатору (например: светодиод), который должен наблюдаться «оператором».

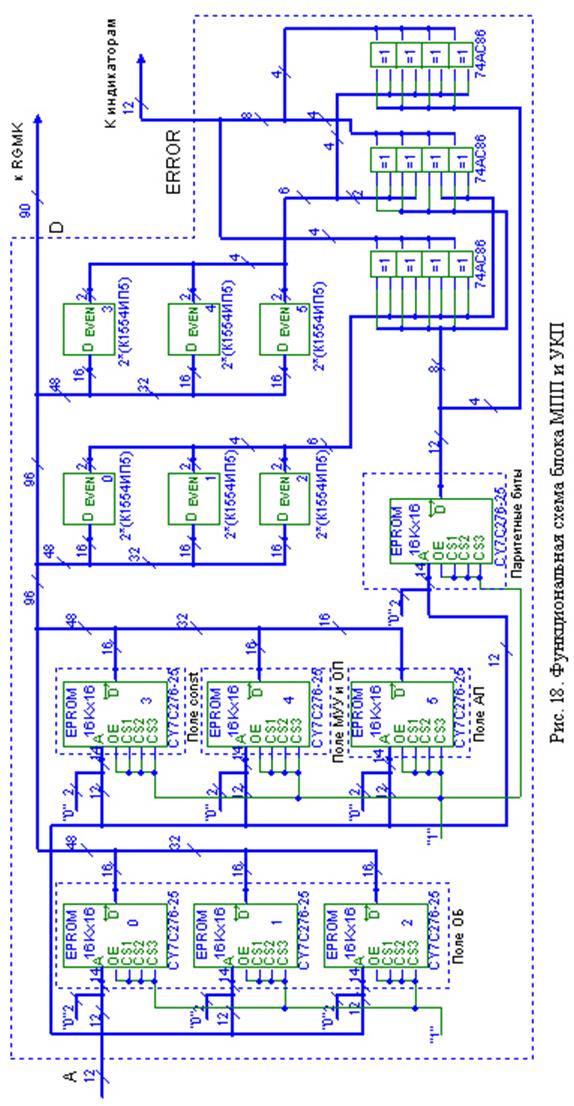

Для удобного изображения функциональной схемы МУУ блок МПП и УКП объединены в один блок. Функциональная схема данного блока приведена на рис. 18.

У данной схемы есть некоторые особенности. Если посмотреть табл. микрокоманды (табл. 2), то можно увидеть зарезервированные поля (обозначенные RESERV) и «остаток» после поля АП в виде 4 битов, при программировании МПП в них необходимо записать нули, т.к. выработка контрольных битов ведётся с учётом этих нулей. Далее же при управлении ядром они не нужны, поэтому в RGMK поступает не 96 битов, а 90 (2 – RESERV + 4 бита после поля АП).

Т.к. организация используемой памяти 16Kx16bit, то в старшие разряды адреса подаются «0», т.е. адресное пространство сокращено до 4Кслов.

На каждые 8 битов МК приходится по одному паритетному, т.е. необходимо всего 12 паритетных битов. ИМС выполняющие свертку объединены поблочно (для удобного отображения).

Так же ИМС памяти пронумерованы в порядке их «расположения» в табл. 2.

Блоки ИМС свертки проиндексированы, в соответствии с порядком сравнения битов ИМС, т.е. 0 –му блоку ИМС сравнения соответствуют 16 – битов ИМС памяти под № 0 и т.д.

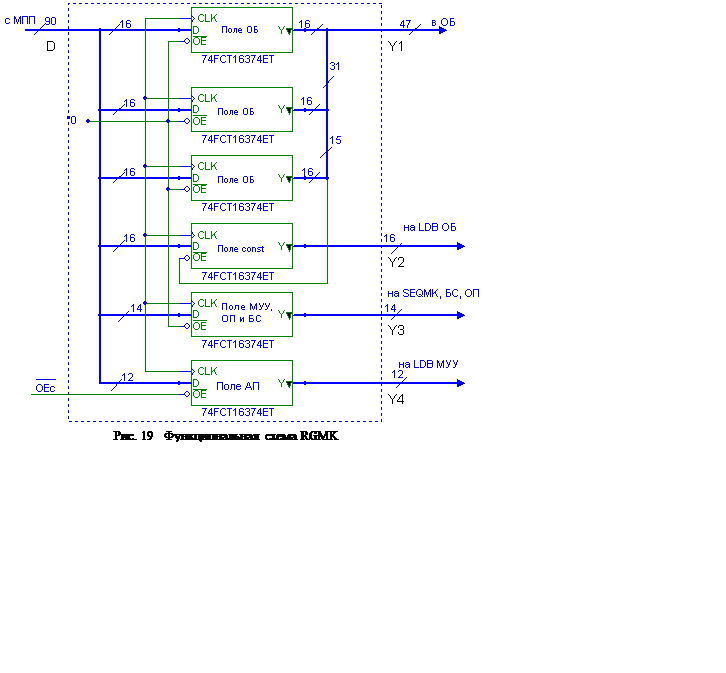

RGMK - конвейерный регистр микрокоманд осуществляет хранение микрокоманды в течение одного цикла. Разрядность регистра равна размеру микроинструкций. Естественно, что RGMK состоит не из одной ИМС. Тем более это удобно тем, что некоторые поля бывают не нужны и их подача вызовет конфликтные ситуации и выход из строя устройств (например: поле const). На рис.19 приведена функциональная схема RGMK. В качестве 16-битного регистра был взят регистр фирмы IDT 74FCT16374ET.

Некоторые особенности данной

функциональной схемы. Как и было отмечено выше в таблице МК (табл.2) есть

резервные поля (RESERV), которые не используются, а созданы для удобного

расположения переменных полей (const,

АП) и лучшего восприятия таблицы. Так вот

RG-ы используемые в данной функциональной схеме

используют только активные поля МК, поэтому не важно что хранится в

«недостающих» битах в RG-ах.

Всё выше сказанное, хорошо будет видно на принципиальной схеме МУУ.

7.3 Функциональная схема МУУ

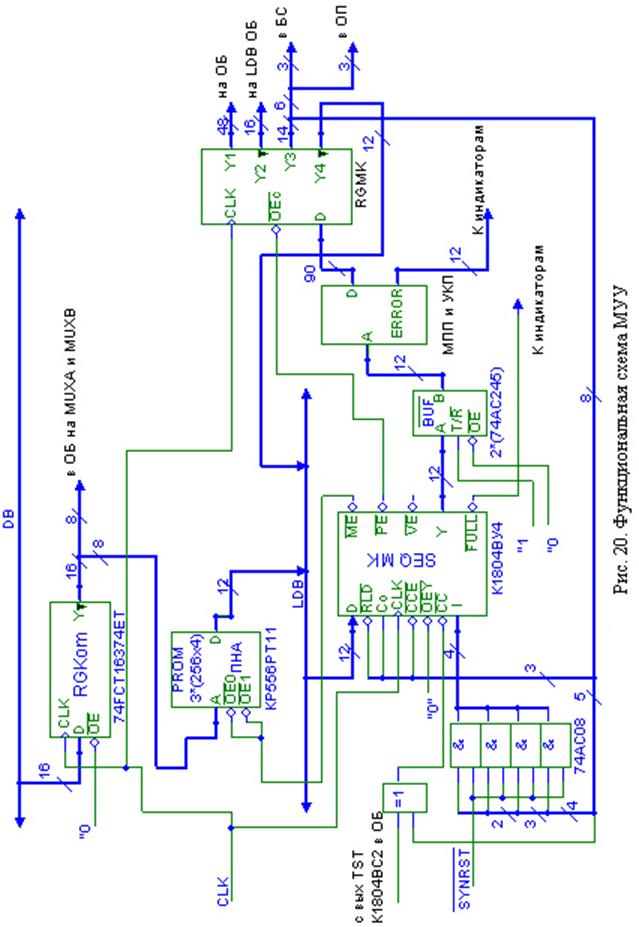

Функциональная схема МУУ приведена на рис. 20.

В качестве RGK взят 16-битный регистр фирмы IDT 74FCT16374ET (время предустановки (su) = 2 ns). В разрешении записи нет необходимости (отрицательная сторона: повышается нагрузка на DB), т.к. после того, как ПНА получил адрес и SEQ загрузил адрес, содержимое регистра больше не нужно и оно может быть изменено с приходом фронта синхросигнала.

ПНА построен на 3-х отечественных ИМС памяти типа PROM КР556РТ11 с организацией 256*4 бит. Кристаллы всегда включены, т.е. память готова к работе в любой момент времени. Входы адресов ИМС соединены параллельно, выводы данных не соединены, что необходимо при наращивании разрядности хранимых данных.

SEQ MK выполнен на ИМС К1804ВУ4. Выход ![]() не

используется в структуре и может быть подключён к панели индикаторов для

отслеживания ситуаций переполнения стека. Вход инструкций подключён через

элементы И с линией

не

используется в структуре и может быть подключён к панели индикаторов для

отслеживания ситуаций переполнения стека. Вход инструкций подключён через

элементы И с линией ![]() для начальной установки МПП в

нулевой адрес (I=0000àY=0000). Подробнее об этом см. п. 8.2.

для начальной установки МПП в

нулевой адрес (I=0000àY=0000). Подробнее об этом см. п. 8.2.

В цепь выход SEQMK и адреса МПП включены буферы фирмы FAIRCHILD 74AC245 [11] для снижения нагрузки на выход Y SEQMK.

Организации МПП, УКП и RGMK описаны выше.

7.4 Краткое описание работы МУУ

Шестнадцать разрядов поступают с шины данных на регистр команд. Восемь старших разрядов идут на ПНА, а восемь младших на мультиплексоры выбора адресов РОН ОБ. Преобразованный адрес с ПНА поступает на секвенсор, который работает с 12-разрядными адресами. Секвенсор адресует МПП. Далее команда фиксируется в регистре микрокоманд откуда, с приходом положительного фронта синхросигнала, подается на устройства, которыми она управляет.

6.5 Расчёт минимально допустимой длительности цикла МУУ

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.