![]() В

данной конвейерной структуре длительность такта оценивается как

В

данной конвейерной структуре длительность такта оценивается как

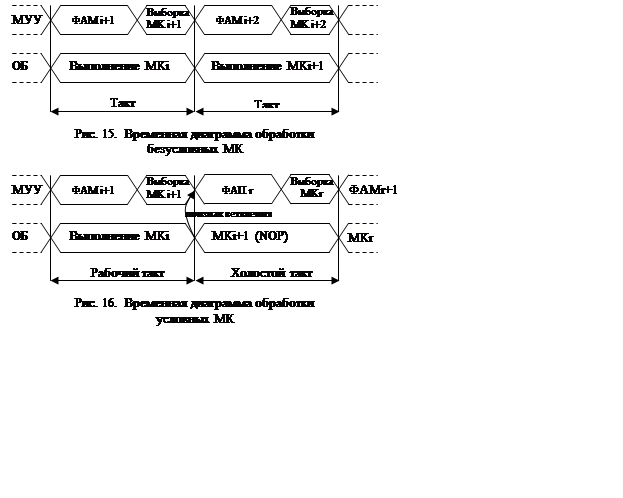

но на организацию условных переходов требуется 2-а такта вместо одного: на первом такте условие вычисляется в ОБ и попадает в SRG, на втором – в ФАМ выполняется условный переход по значению условия, получаемому из SRG. Выше сказанное необходимо продемонстрировать на временных диаграммах обработки МК.

Такая

структурная организация в независимости от характеристик алгоритма обладает

наибольшим быстродействием, если ![]()

6.2 Структурное описание МУУ

Первый

уровень структурного описания МУУ представляется как взаимодействие МУУ в системе

управляющей части микропроцессора (рис. 8).

Первый

уровень структурного описания МУУ представляется как взаимодействие МУУ в системе

управляющей части микропроцессора (рис. 8).

Из рис.8 видно, что взаимодействие МУУ с другими элементами системы осуществляется через шину DB, линии инструкций и через линию «статус».

Некоторые поля инструкций(const, адрес перехода) необходимо запрещать на вывод, что необходимо учесть при конструировании RGMK.

Для одновременной работы устройств МУУ необходим системный синхросигнал.

После выяснения общей структурной схемы можно “опускаться” на более низкий уровень структурного описания, т.е. рассмотрение внутренней организации МУУ.

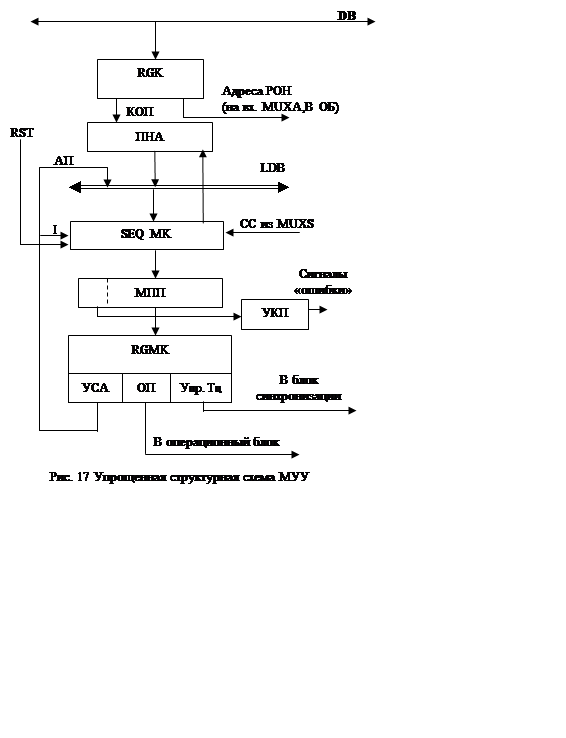

Пояснения к рис. 17:

RGK – регистр команд

КОП – код операции

ПНА – преобразователь начального адреса

SEQ MK – секвенсор микрокоманд

АП – адрес перехода

I – инструкции управления SEQ MK.

МПП – микропрограммная память

УКП –устройство контроля паритета

RGMK – регистр микрокоманд

УСА – установка следующего адреса

ОП – поле управления операционными ресурсами(ОБ)

Упр. Тц – управление длительностью цикла

CC – код ветвления(статус).

В принципе, структурная схема проста, но всё же необходимо пояснить (в вкратце) назначение элементов.

RGK получает с DB команду (код операции + адреса операндов). Операнды передаются в ОБ на мультиплексоры выбора источника адреса для РОН, а код операции поступает на адресный вход ПНА. В соответствии с форматом команд поле «код операции» (КОП) занимает 8 бит, следовательно разрядность адреса ПНА равна 8.

Преобразователь начального адреса(ПНА) служит для получения адреса микропрограммы обработки команды, код которой получен из RGK. Выбранные данные (адрес для SEQ) поступают на вход D SEQMK. SEQMK построен на БИС К1804ВУ4 имеющей 12-разрядный вход D. Таким образом организация памяти должна быть 256x12bit. В данной работе используется память типа PROM.

SEQ MK необходим для адресации МПП. SEQ MK генерирует следующий адрес в зависимости от поданных на него инструкций, АП или адреса с ПНА и кода ветвления (при организации условного перехода), подающегося с MUXS (рис. 10) операционного блока. БИС К1804ВУ4 предоставляет широкие возможности по адресации МПП.

МПП необходима для хранения микрокоманд (управляющих слов). Соответственно разрядность адреса должна быть 12 (выход SEQMK 12-разрядный), а разрядность данных должна соответствовать длинне микрокоманды (табл. 2) + каждым 8 битам МК должен соответствовать 1 паритетный бит. Паритетные биты записываются в конец МК. Таким образом организация памяти должна быть 4K x (размер МК + биты паритета) bit. Устройство программатор для пользователя, не разрабатывалось, поэтому целесообразно использовать память типа EPROM, что необходимо учесть при разработке конечного продукта, т.е. сделать возможным извлечение ИМС памяти из системной платы для дальнейшего перепрограммирования. В качестве такой ИМС памяти взяты ИМС EPROM фирмы Cypress CY7C276-25 с организацией 16Kx16bit. Это не совсем та организация, которая нужна, но в целях упрощения структурной и принципиальной схем было принято такое решение. Использование ИМС 4Kx8bit (например CY7C243) увеличивает число использованных ИМС в 2 раза, что не совсем эффективно (14 ИМС против 7).

Устройство контроля паритета (УКП) необходимо для контроля правильной работоспособности МПП. Свертка по модулю 2 осуществляется микросхемой КР1554ИП5. После свертки бит четности и паритетный бит попадают на схему Искл.ИЛИ, где и генерируется бит ошибки, если произошла ошибка. Для удобства устранения ошибок (замены неисправных ИМС) каждой ИМС памяти соответствует своя «линия ошибки».

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.