DB - шина данных

AB - шина адреса

Линии 7 и 8 составляют шину управления (CB).

Собственно, начать анализировать обобщённую структурную схему ядра (рис.3) стоит с рассмотрения принципа микропрограммного управления сформулированного Уилксом в 1961 году.

Принцип микропрограммного управления заключается в хранении управляющих слов, выполняющих элементарные действия в течении цикла, и выборки их с помощью секвенсора (SEQ). На этом принципе и основывается конструируемое ядро.

Таким образом МУУ хранит в микропрограммной памяти(МПП) и выбирает управляющие слова (т.е. МК) из МПП, передаёт их в качестве управляющих слов ОБ и БС. Естественно, принимая управляющие слова, устройствами выполняются соответствующие инструкции.

Работа с ОП осуществляется через ОБ. ОБ вычисляет адрес ячейки для чтения/записи и принимает/передаёт данные из/в ОП.

Естественно, что ОБ может принимать/передавать данные не только из/в ОП, но и с/в внешних/ие устройств/а по шине данных (DB).

Блок синхронизации необходим для формирования системного синхросигнала (CLK), а также формирования синхронного сигнала сброса (RESET).

Длительность цикла синхросигнала управляется МУУ, с целью уменьшения затрат времени на «короткие» операции.

После рассмотрения обобщенной структурной схемы ядра можно спускаться на нижние уровни схемного описания системы.

5.1 Структурное описание ОБ

Первый уровень представления операционного блока, как элемента системы, представляется как взаимодействие ОБ в системе операционной части микропроцессора (рис. 8).

Из рис.8 видно, что взаимодействие ОБ с другими

элементами системы осуществляется через 2-е шины, DB и AB,

управление ОБ осуществляется МУУ, ОБ так же может влиять через линию «статус»

на формирование следующего адреса микропрограммы(МП) (код ветвления). К DB и AB могут

подключаться другие устройства, для этого необходимо, чтобы выходы данных ОБ

имели тристабильные состояния, которые должны управляться входами разрешения ![]() , т.е. из

полей микрокоманды (МК). Разрешение записи в RGDin необходимо для снижения нагрузки на DB, т.е.

на устройства работающие на ней.

, т.е. из

полей микрокоманды (МК). Разрешение записи в RGDin необходимо для снижения нагрузки на DB, т.е.

на устройства работающие на ней.

Для одновременной работы устройств ОБ необходим системный синхросигнал.

|

низкий уровень структурного описания.

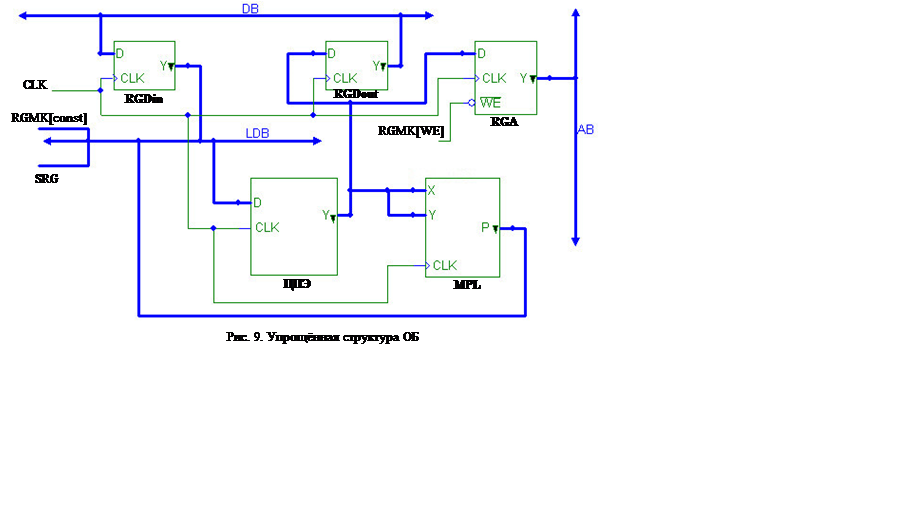

Анализируя рис.9 можно понять, что взаимодействие с AB и DB осуществляется через регистры с динамическим управлением по положительному фронту синхросигнала. Они должны иметь входы разрешение на запись и на чтение, т.е. в МК должны быть биты для управления ими. Загрузка данных в ОБ может осуществиться из 4-х источников: RGMK[const], SRG, RGDin и P (результат вычисления MPL), в свою очередь выбор источника загрузки должен производиться из отведённых битов в МК.

ОБ производит операции над данными или адресами, поэтому выход Y ОБ подключён к RGout, RGA и входам данных MPL. Соответственно, необходимо отключать RGA и MPL, если загрузка ведётся на DB и т.д., что необходимо отразить в битовых полях МК.

Такое подключение MPL обеспечивает оперативную подачу данных в ОБ в обход DB (если необходимо сохранить результат операции в РОН ОБ), что в свою очередь экономит количество циклов на данную операцию, по сравнению с альтернативным путем MPLà DB à RGDin à ЦПЭ. Если же необходимо передать результат вычислений MPL в DB, необходимо совершить простую пересылку через ОБ на шину данных.

Для построения ОБ так же необходимо спуститься ещё на один уровень, на уровень построения ЦПЭ. Это необходимо для понимания того, чем нужно «обвязать» каскадированные МПС.

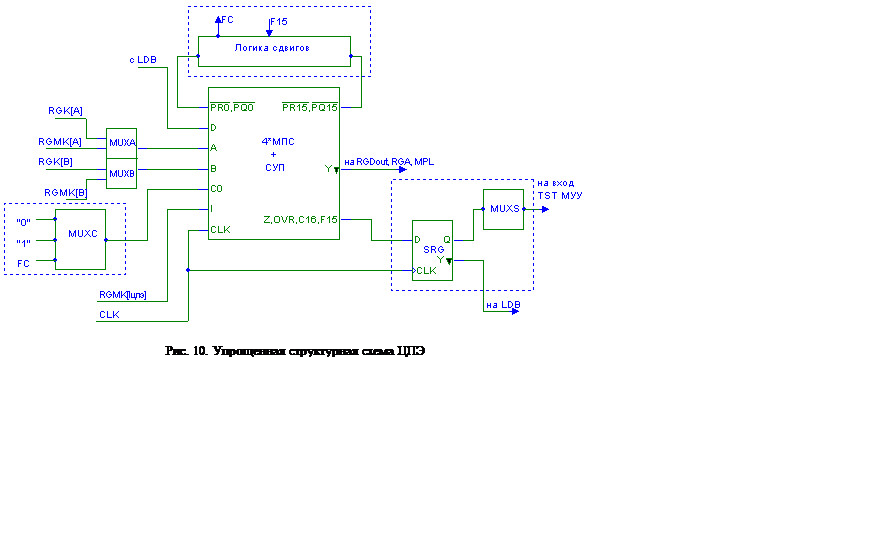

Предусмотрено сохранение словосостояния. MUXS

выполняет роль селектора кода ветвления. В принципе, структурная схема проста и

не требует объяснений. Особенностью принимаемой в разработке БИС К1804ВР2 [14]

является, то что она содержит MUXC,

логику сдвигов, SRG и MUXS

(на рис.10 выделены штриховой линией), что сильно упрощает разработку принципиальной схемы ядра и разводку

схемной платы в конечном итоге.

5.2 Каскадирование МПС

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.