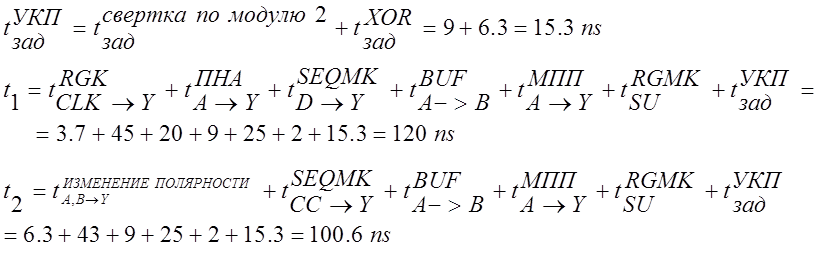

При оценке длительности цикла, отыскивается так называемый критический путь распространения сигнала (тракт), который вносит минимальную задержку. Для нахождения такого тракта рассматриваются наиболее длинные тракты, последовательно оценивая для каждого из них задержки, вносимые отдельными элементами.

Из

данного анализа видно, что максимальная задержка составляет 120нс. Следовательно, соотношение ![]() (149.2 ns> 120 ns) соблюдается, что означает, что данная структура будет

работать наиболее эффективно.

(149.2 ns> 120 ns) соблюдается, что означает, что данная структура будет

работать наиболее эффективно.

7.1. Структурное описание ОП

Первый уровень структурного описания основной памяти(ОП) представляется как взаимодействие ОП в системе микропроцессора (рис. 8).

Из рис. 8 видно, что взаимодействие ОП с другими элементами системы осуществляется через шину DB, AB и через линию инструкций с МУУ. При разработке ОБ учитывалось, что используется память асинхронного типа, что означает отсутствие в ИМС памяти RG –ов адреса и данных.

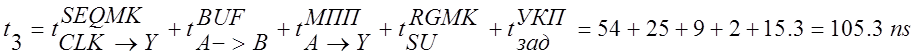

На рис.21 представленная структурная схема основной памяти. Необходимо дать функциональное определение каждому элементу.

Буферы адреса снижают нагрузку на AB, в конечном итоге на RGA. Переход в Z-состояние и двунаправленная передача не нужны.

Дешифратор выбора устройств необходим для выбора типа памяти. При выборе используются 2-а старших бита адреса (15 и 16). При этом «остаются свободными» 2-а выхода дешифратора. Их можно использовать для выбора других блоков памяти.

Блоки памяти:

Размер данных хранимых в ОП равен 16. В задание указано, что необходимо реализовать память 2-х типов: EPROM и SRAM емкостью 128Kbit. Т.о. организация блоков памяти должна быть 8Kx16bit.

В данной работе используются ИМС памяти зарубежного производства:

- EPROM – построена на 2-x ИМС фирмы CYPRESS CY7C263-20 с организацией 8Кх8 бит и временем доступа 20ns [9].

- SRAM - построена на 2-х ИМС фирмы IDT 7164S15 с организацией 8Кх8 бит и временем доступа 15 ns [8].

Как видно из предложенной элементной базы «наращивать» адресное пространство не понадобится, необходимо только «нарастить» разрядность хранимых данных, что осуществляется при параллельном соединении входов ИМС (одного типа).

Для снижения нагрузки на выходы ИМС памяти и предотвращения конфликтов на DB применены буферы. Причём на шину DB необходимо включить двунаправленные буферы с возможностью перехода в Z-состояние, т.к. данные могут передаваться как на запись, так и на чтение.

Управление

памятью осуществляется 2-я битами МК. ![]() –

разрешение записи в блок памяти SRAM и

–

разрешение записи в блок памяти SRAM и ![]() -разрешение

работы с памятью (разрешает функционирование дешифратора выбора устройства).

-разрешение

работы с памятью (разрешает функционирование дешифратора выбора устройства).

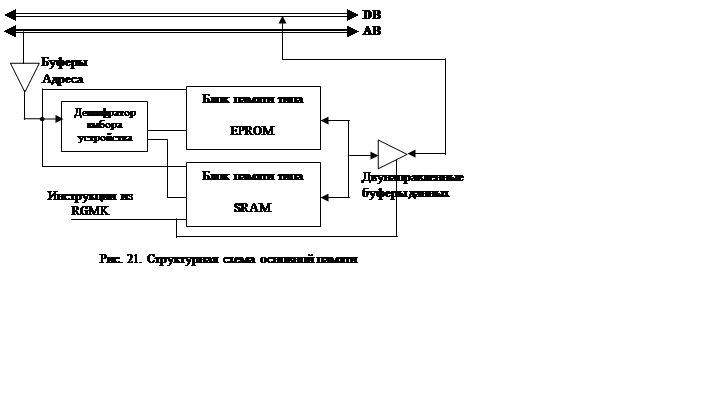

7.2 Функциональная схема основной памяти

Исходя из выше сказанного можно составить функциональную схему блока основной

памяти (рис. 22).

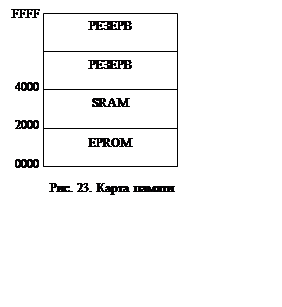

Выбор

типа памяти осуществляется 15 и 16 битами адреса, т.е. могут подключится ещё

2-а блока с памятью. Выше сказанное можно наглядно продемонстрировать на карте

памяти (рис. 23). Для выбора типа памяти используется DC 2à4 зарубежной фирмы

FAIRCHILD 74AC139 [11] (с временем задержки по адресным

входам 6 ns) выходы, которого соединены с входами ИМС

выбора кристалла ![]() . На вход

разрешения работы дешифратора подаётся бит МК

. На вход

разрешения работы дешифратора подаётся бит МК ![]() .

.

Так

же бит

Так

же бит ![]() переводит выходные буферы в Z-состояние дабы

избежать порчу устройств подключённых к DB.

переводит выходные буферы в Z-состояние дабы

избежать порчу устройств подключённых к DB.

В качестве буфера данных/адреса используется восьмиразрядные двунаправленные буферы фирмы FAIRCHILD 74AC245 [11], которые обеспечивают возможность чтения, записи и переход в Z-состояние.

14 – бит адреса не используется.

Бит МК ![]() управляет переходом

блока статической памяти в режим записи, а выходные буферы изменяют направление

пропускания данных.

управляет переходом

блока статической памяти в режим записи, а выходные буферы изменяют направление

пропускания данных.

При разработке схемной платы необходимо учесть особенности программирования памяти типа EPROM, т.е. сделать возможным извлечение ИМС памяти с системной платы для дальнейшего её перепрограммирования.

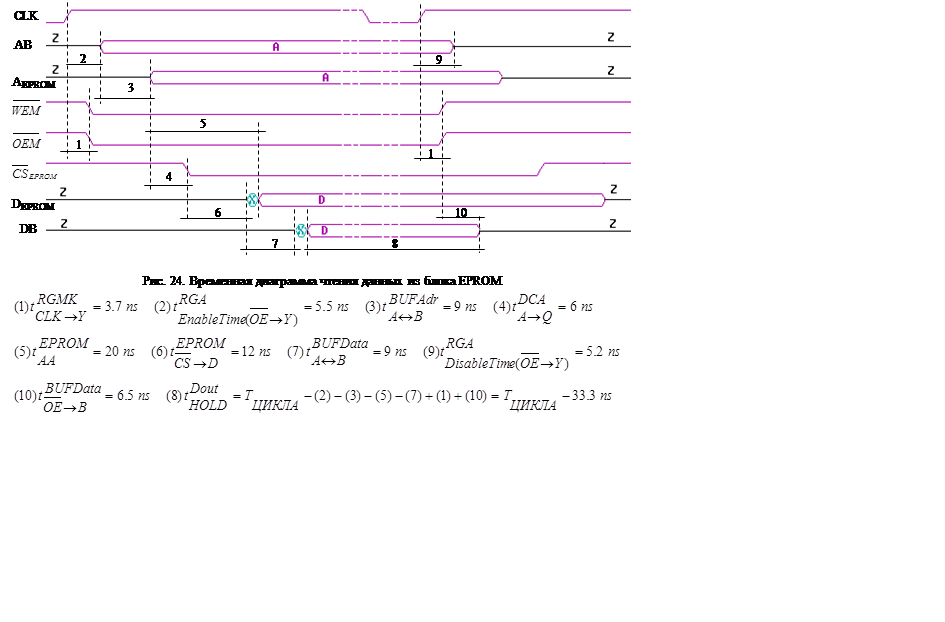

7.3. Временные диаграммы работы основной памяти

Блок памяти EPROM

Чтение

(![]() = H)

= H)

Примечание: на

последующих временных диаграммах некоторые временные задержки идентичны выше

приведённым (например:  ), поэтому

подписываются только новые значения.

), поэтому

подписываются только новые значения.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.