Кафедра вычислительной техники

|

Курсовой проект

по дисциплине «Схемотехника»

Факультет: АВТ

Группа : АМ-211

Студент : Слуцкий А.А.

Преподаватель: Соболев В.И.

Содержание.

Стр.

Постановка задачи. 3

Индивидуальные исходные данные 3

Обобщенная структура ядра микро ЭВМ. 4

1. Формат команд. 4

2. Формат данных. 6

3. Разработка структуры операционного блока. 7

- Расчет времени цикла ОБ. 8

4. Микропрограммное устройство управления . 9

- Расчет времени цикла МУУ 12

5. Основная память. 12

- Временные диаграммы чтения/записи ОП 15

6. Формат микрокоманды 16

7. Примеры выполнения команд 17

8. Разработка блока синхронизации микроЭВМ. 18

9. Разработка схемы начальной установки. 19

11. Список литературы. 22

Постановка задачи.

Задача данного курсового проекта заключается в разработке прототипа ядра микроЭВМ. Основные требования, к которому заключаются в:

· Высоком быстродействии (производительности)

· Простоте и надежности схемных решений

Под надежностью понимается отсутствие в схемах критических временных соотношений, риска сбоя и гонок сигналов, использование унифицированных способов обмена между устройствами и т.п.

Индивидуальные исходные данные.

Состав, элементная база и разрядность операционного блока:

Процессорный модуль: КА1843ВС1, КА1843ИР1

Разрядность ПМ: 32 бит

Требования к микропрограммному устройству управления:

Секвенсор микрокоманд: КА1804ВУ4

Разрядность секвенсора: 12 бит

Функциональный состав и ёмкость основной памяти:

SRAM: 1M

EEPROM: 2М

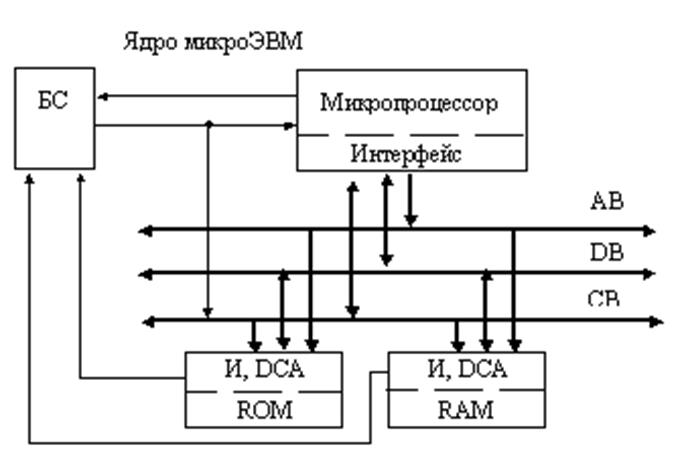

Обобщенная структура ядра МикроЭВМ.

Рис.1

В процессе выполнения курсового проекта необходимо спроектировать ядро МикроЭВМ.

Процесс можно разделить на следующие этапы:

· Разработка структурной схемы микропроцессора (ОБ, МУУ).

· Разработка основной памяти: ROM (EEPROM), RAM (SRAM).

· Разработка (проектирование) блока синхронизации.

· Проектирование схемы начальных установок.

· Разработка принципиальной схемы памяти.

Формат команд.

Команда состоит из одного или двух 32-разрядных слов и должна размещаться в основной памяти с соблюдением требований целочисленных границ слов.

Поддерживаются следующие команды:

1) регистр - регистр;

2) регистр - память;

3) память - регистр;

4) операции ветвления и переходов.

|

КОП |

RG1 |

RG2 |

P |

W |

31 2322 1716 1110 5 4 0

31 2322 1716 1110 5 4 0

|

КОП |

X1 |

RG2 |

P |

W |

31 0

Data |

31 2322 1716 1110 5 4 0

|

КОП |

RG1 |

X2 |

P |

W |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.