31 0

Data |

31 2322 0

|

КОП |

Не используется |

31 0

Data |

Описание полей команд:

32-х разрядная команда состоит из 5-ти полей. В младших 5-ти разрядах (4..0 бит) расположено поле задания ширины байтового поля для операндов, представляющих собой битовые поля переменной ширины. Затем расположено 6-ти разрядное (10..5 биты) поле задания направления и величины сдвига для сдвиговых операций или позиция для операндов, представляющие собой битовые поля переменной ширины. Далее следуют два 6-ти разрядных поля (22..17 биты регистра источника/приемника и 16..11 биты регистра источника), которые определяют адреса используемых в команде регистров. Такое количество бит позволяет адресовать любой из 64-х регистров. В старших 8 разрядах размещается поле кода операции (КОП). Код операции позволяет идентифицировать одну из 256 различных команд. Самый же старший бит – резервное поле включен в код операции для возможного расширения количества команд. В зависимости от КОП поля RG1 , RG2 , P и W команды могут быть не использованы. Поля RG1 или RG2 могут быть заменены на соответствующие им поля X1 или X2 в зависимости от типа команды. Поля X1 и X2 – поля РОН содержащие адрес ячейки памяти.

В 64-х разрядной команде первое слово полностью соответствует 32-х разрядной команде. Второе слово представляет собой 32-х разрядное поле Data, которое может содержать либо смещение адреса ячейки памяти, либо непосредственный адрес ячейки памяти, либо непосредственно данные в зависимости от КОП.

Формат данных.

Данные имеют формат 32 бита и хранятся в памяти в виде 32 разрядных слов, при считывании из памяти и записи в память действия производятся над 32-х разрядным словом.

Типы данных, поддерживаемые данным ядром:

1. целые двоичные;

2. двоично-кодированные десятичные;

3. битовые поля переменной ширины.

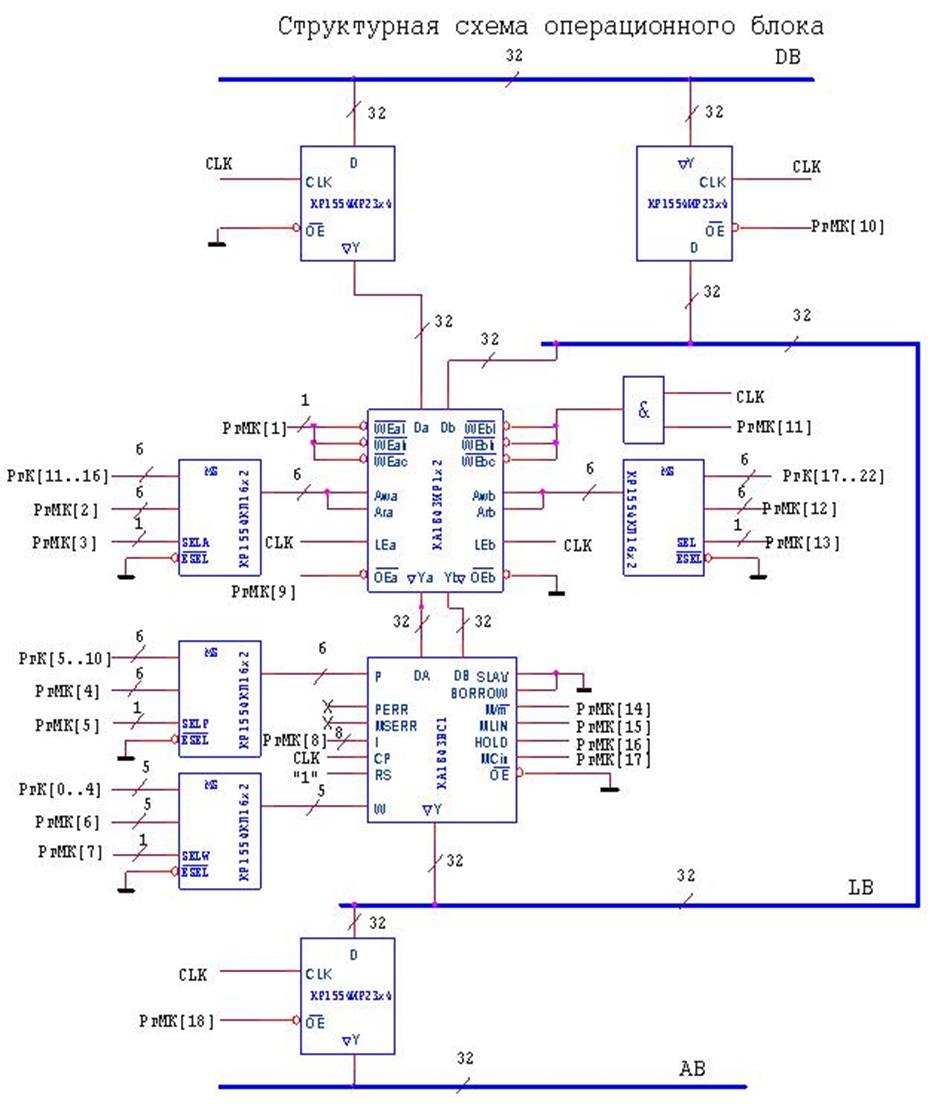

Разработка структуры ОБ.

Рис 2

ОБ состоит из микропроцессорной секции КА1843ВС1, регистрового файла КА1843ИР1, регистров: адресного, регистров входных и выходных данных (см. приложении1).

Микропроцессорная секция КА1843ВС1 представляет собой нерасширяемый 32-х разрядный процессорный модуль. СБИС КА1843ВС1 содержит трехвходовое комбинационное АЛУ. Данное СБИС имеет два входных и один выходной порты данных. Регистровый файл отделен от ЦПЭ. А также микропроцессорная секция оснащена внутренней логикой сдвигов и имеет развитые встроенные средства контроля ошибок.

Регистровый файл КА1843ИР1 представляет собой 4-х портовую регистровую память, два порта записи и два порта считывания, с двухсторонним доступом, а также четыре 6-ти битовых адресных порта. Регистровый файл имеет внутреннюю организацию 64х18 бит.

Выходные порты (по записи и по чтению) соединены с соответствующими входами МПС. Многопортовая организация и развитое управление прибора позволяет выполнять два чтения и две записи за один цикл.

В качестве регистров входных/выходных данных и регистра адреса памяти используются регистры КР1554ИР23. Выходы у этого регистра с тремя состояниями, это обеспечивает возможность отключения его от локальной шины данных. Это необходимо для избежания выхода из строя выходных каскадов устройства, так как кроме регистра входных данных на локальную шину работают попеременно еще несколько источников.

Данные для ОБ фиксируются в регистре входных данных, затем они поступают на входы МПС (если разрешен вывод из регистрового файла) пройдя через нее, попадают на локальную шину данных, т.к. всегда разрешен вывод из МПС. Это обусловлено тем, что источником данных на локальной шине может быть только МПС. С локальной шины данных после выполненной операции данные поступают в выходной регистр, регистр адреса или сохраняются в регистровом файле.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.