Реакция на сигнал общего сброса. По приходу активного сигнала #RST происходит перевод выхода данных микросхем ПНА в Z-состояние и локальная шина данных освобождается для пересылки адреса из регистра микрокоманд в секвенсор; синхронный (с сигналом CLK) сигнал SYNRST сбрасывает в «0000» инструкцию секвенсора. Дальнейшие действия: выдача секвенсором нулевого адреса, выборка микрокоманды инициализации из нулевого адреса МПП, установка микрокоманды в регистре микрокоманд. В следующем такте биты микрокоманды переведут все микросхемы в оптимальное состояние. Кстати, данная операция будет повторяться многократно, пока не закончится подача низкого сигнала SYNRST. И только по его высокому уровню секвенсор будет в состоянии выдать адрес, отличный от 0.

Расчет минимальной длительности цикла МУУ.

Как и при расчете минимальной длительности цикла ОБ, рассмотрим разные тракты прохождения сигнала, отыскивая критический путь. Наиболее длинные пути приведены ниже

Блок микропрограммного управления. Имеется большой набор операций:

·

загрузка

нового адреса через регистр КОП

tзр(РКОП)+ tзр(

ПНА)+ tзр(SEQ)+ tзр(МПП)+

tзр(RGMK)

=5,2 + 45 + 20 +20 + 4,5 = 94,5 нс

·

загрузка

нового адреса из регистра микрокоманд

tзр(RGMK)+ tзр(SEQ)+ tзр(МПП)+

tзр(RGMK) =

10,5 + 20 +20 +4,5 = 55 нс;

·

условный

переход

tзр(RGMK)è tзр(СС)è tзр (Адрес(SEQ))è tзр (МПП)è tзр (RGMK)=

10,5 + 43 +20 +4,5 = 78;

· Последовательный счёт (использование внутреннего счётчика) tзр(RGMK)+tзр(SEQ)+tва(МПП)+tsu(RGMK)=10.5нс+125нс+20нс+4.5нс=160нс,

Следовательно, длительность минимального цикла составляет 160нс, что удовлетворяет условию: t Ц.MAX.ОБ ³ t Ц.MAX.МУУ. Поэтому выбранный вариант компоновки МУУ будем считать верным, и примем его в качестве окончательного варианта.

Основная память

Используемые типонаминалы микросхем:

Flash - AM29F032B

Организация памяти:32 Megabit (4 M x 8-Bit)

SRAM - CY7C1041BV33 фирмы-производителя Cypress

Организация памяти: 256K x 16 Static RAM

BUF :

AB, CB - 54174FCT16244T 16bit Buffer/Line Driver

DB - 54174FCT16245T BiDirectional Transceiver

Карта основной памяти

Адреса Flash располагаются в нижней области адресов, а адреса SRAM - в верхней.

FFFFFFF

![]()

![]()

![]() ……….

……….

1BFFFFF

1BFFFFFFLASH_1-я стр.

1800000

……….

![]() 17FFFFF

17FFFFF

FLASH_2-я стр.

1400000

![]() ……….

……….

SRAM

![]()

![]() C00000

C00000

………..

![]() 000000

000000

Рис.4. Карта памяти.

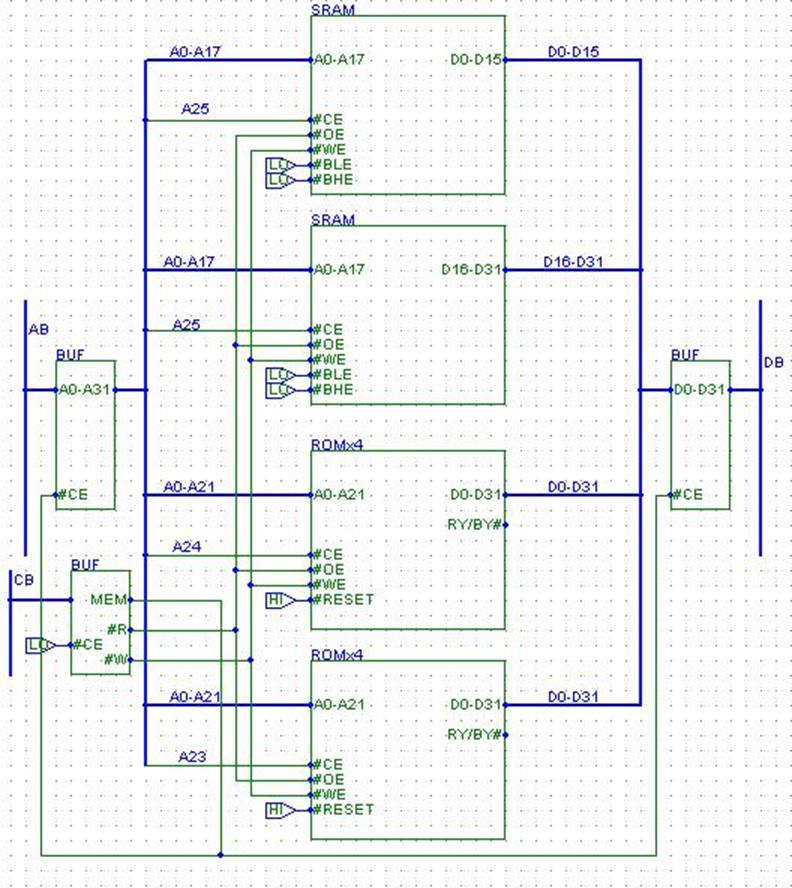

Принципиальную схема памяти.

Рис 5

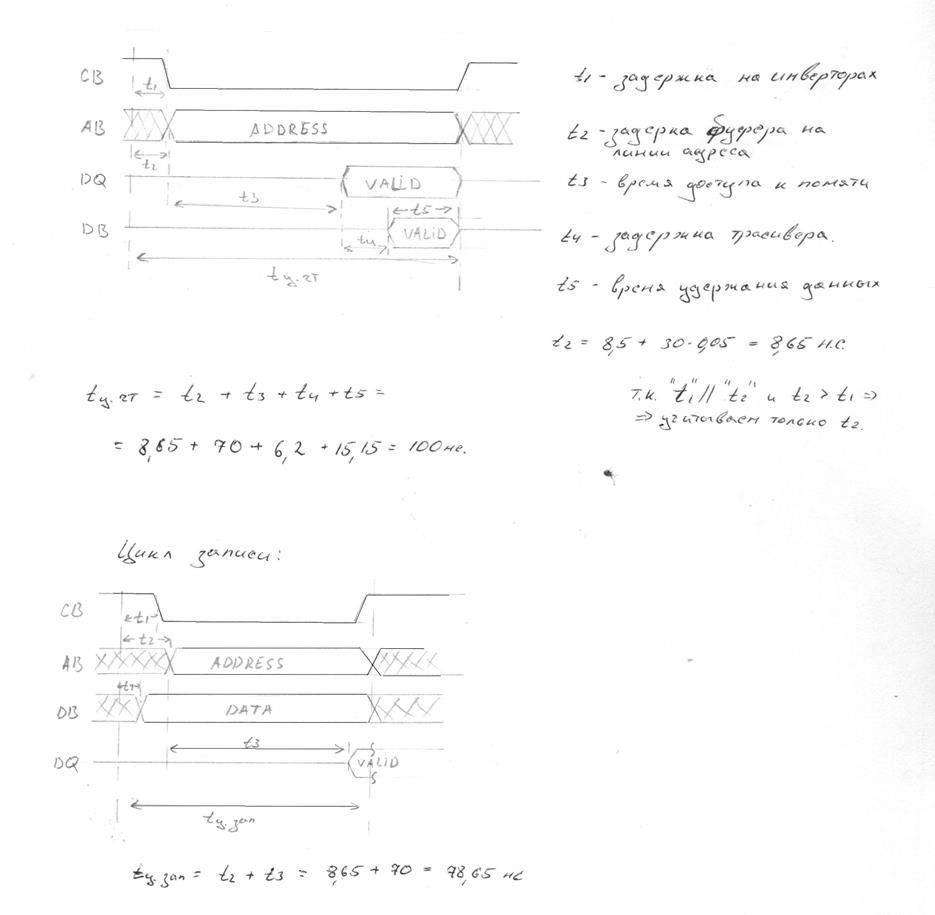

Расчет минимальной длительности цикла памяти

Формат микрокоманды.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.