Данные (флаги состояния) могут попасть напрямую из АЛУ при RS=L, либо при RS=H выбираются на шину Y из статусного регистра, а затем могут попасть на локальную шину данных, что обеспечивает сохранение и восстановление значений флагов состояний.

Структурную схему ОБ см. в приложении 1.

Расчёт времени цикла ОБ.

Время цикла ОБ (максимальное) вычисляется по одному из следующих путей:

1. Тц = RGDin(tз cp->Dout)+RGF(tз Da -> Ya)+MPS(tз Da/Db->Y)+РАП(tSU)=10,5+33*2,5+35*2,5+5=10,5+82,5+87,5+5=185,5 нс;

2. Тц = RGDin(tз cp->Dout)+RGF(tз Da -> Ya)+MPS(tз Da/Db->Y)+RGF(tдоступа)=10,5+33*2,5+35*2,5+24*2,5=10,5+82,5+87,5+60=240,5 нс;

3. Тц = RGDin(tз cp->Dout)+RGF(tз Da -> Ya)+MPS(tз Da/Db->C,Z,N,V,L)=10,5+82,5+43*2,5=92,5+107,5=200,5 нс;

4. Тц = RGМK(tз cp->Dout)+2ИНЕ(tзр I->O)+RGF(tз WEa->Ya)+MPS(tз Da/Db->Y)+RGF(tдоступа)=10,5+8,5+32*2,5+35*2,5+24*2,5=19+80+87,5+60=246,5 нс.

Таким образом, Тц (время цикла операционного блока) = 246,5 нс.

Разработка структуры микропрограммного устройства управления (МУУ).

Компоновка МУУ.

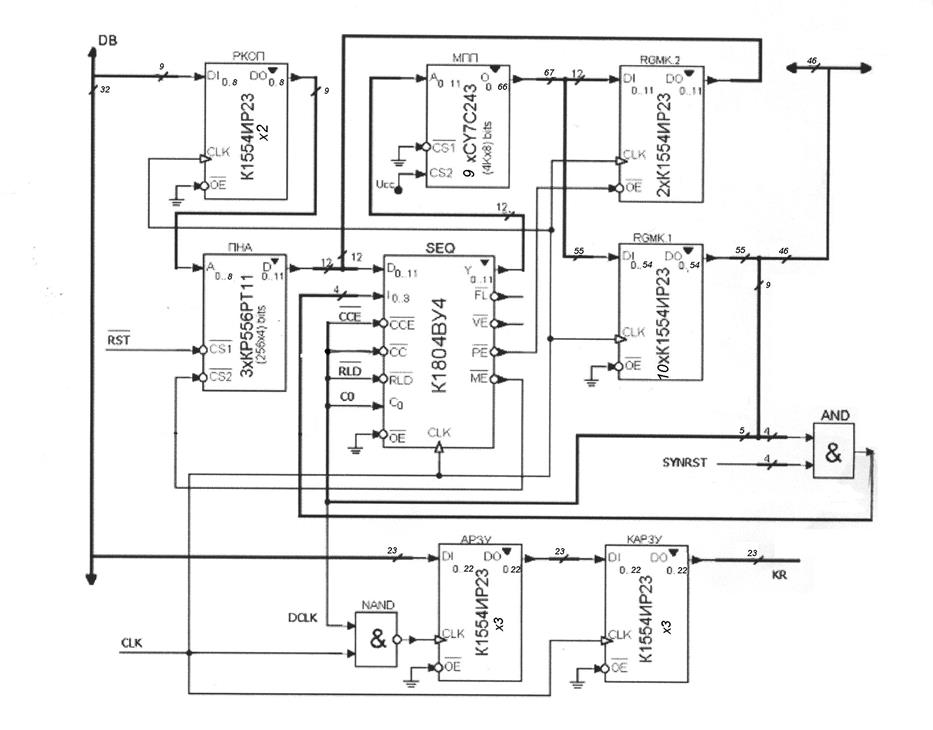

Рис 3

РКОП (КР1554ИР23). Регистр, хранящий в течение такта код операции. Он необходим для адресации ПНА. После того, как ПНА получил адрес и SEQ этот адрес загрузил, содержимое РКОП больше не нужно и оно может быть изменено с приходом фронта синхросигнала.

ПНА (КР556РТ11) . Преобразователь начального адреса служит для получения адреса микропрограммы обработки команды, код которой получен из РКОП. Следует отметить, что при наличии активного высокого сигнала #RST выход памяти находится в третьем состоянии, чем обеспечивается бесконфликтная ситуация на локальной шине данных во время принудительной загрузки адреса начала микропрограммы инициализации.

Секвенсор SEQ (К1804ВУ4) . Получает набор битов управляющей информации и генерирует следующий адрес микропрограммной памяти. Может загрузить 12-ти разрядный адрес, может хранить адрес в стеке (или в счётчике, если нет переноса C0). Может генерировать адрес последовательным счётом. Кроме того, генерирует сигналы разрешения #PE, #ME, #VE, которые используются устройствами МПП и RGMK.2 для согласования вывода адреса в циклах принудительной загрузки адреса.

AND (КР1533ЛИ1). Элемент, выполняющий булеву функцию «И» для двух сигналов, служит для принудительного сброса инструкции SEQ в «0000» при наличии активного низкого уровня сигнала синхронного сброса.

МПП (CY7C243) Микропрограммная память хранит микропрограммы обработки команд более высокого уровня (уровня программирования в машинных кодах) в виде инструкций ко всем устройствам микроЭВМ, которые поддерживают микропрограммное управление.

RGMK (КР1554ИР23). Конвейерный регистр микрокоманды осуществляет хранение микрокоманды в течение одного цикла. Состоит из двух групп: одна из них (RGMK.2) имеет право выводить содержимое, если секвенсор разрешил активным сигналом #PE. Иначе выход находится в третьем состоянии.

АРЗУ (КР1554ИР23). Регистр адреса регистра в РЗУ процессора. Обязан хранить этот адрес до момента следующей действительной команды на системной шине данных. Поэтому я применил условное тактирование регистра с использованием синхросигнала #CLK (инверсный синхросигнал) и сигнала разрешения тактирования DCLK.

NAND (КР1533ЛА3). Осуществляющий комбинацию сигналов элемент «И-НЕ»; служит для условного тактирования регистра АРЗУ.

КАРЗУ (КР1554ИР23). Конвейерный регистр адреса регистра в РЗУ процессора необходим для согласования реакции центрального процессора на операцию и операнды. Его необходимость обоснована тем, что сигнал по тракту РКОПèПНАèSEQèМППèRGMK пройдёт за 2 такта (конвейер первого порядка), и при наличии КАРЗУ прохождение сигнала АРЗУèКАРЗУ осуществляется также за 2 такта. Таким образом, код операции, преобразованный в инструкцию для CPU, и адрес регистра в регистровом запоминающем устройстве придут в одном такте. При отсутствии КАРЗУ адрес регистра прибудет раньше на такт и результат обработки данных в CPU нельзя предсказать.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.