Факультет: АВТ

Группа: АМ – 210

Вариант: 11; 7.

Студент: Финагеев К.С.

Преподаватель: Соболев В. И.

Оглавление

стр.

1.Цель работы…..…………………………………………………………………………………3

2.Цель разработки………………………………………………………………………………...3

3.Исходные данные…………………………………………………………………………..…..3

4.Формат команд…….………………………………………………………………….…….…..4

5. Форматы данных………………………………………………………………………………5

6.Разработка структуры ОБ ……………………………………………………………………..5

5.1.Особенности каскада МПС…………………………………………………………..6

5.2.Особенности использования MPL…………………………………….………..……6

5.3.Формат статусного регистра…………………………………………….………..….6

5.4.Логика сдвигов……………………………………………………………….…….…7

5.5. Расчет минимального времени цикла ОБ…………………………………….…….8

6.Разработка МУУ……………………... …………………………………………….……..…...8

6.1. Принцип работы МУУ……………...……………………………………………….8

6.2 Расчет минимальной длительности цикла МУУ…………………………………...9

7.Разработка основной памяти………………….………………………………………...…..13

7.1.Исходные данные……………………………………………………………….....13

7.2.Описание разработки основной памяти……………………………………….…13

7.3.Выбор интерфейсных элементов………………………………………………....15

8.Расчет длительности цикла ядра микроЭВМ……………………………………………….10

9.Блок синхронизации (БС) и схема начальной установки (СНА)……………………….….10

8.1Схема включения КМ1804ГГ1………………………………………………….…..11

10.Формат микрокоманды………………………………………………………………….....12

11. Построение временных диаграмм работы памяти ………………………………………16

12.Выводы ………………………………………………………………………………………18

13.Список использованной литературы……………………………………………………….19

· Освоение элементов методологии проектирования аппаратных средств

вычислительной техники;

· приобретение практического опыта разработки функциональных устройств и узлов,

выполнение схемотехнических расчетов и оформление схемной документации;

· закрепление и углубление знаний о современной элементной базе.

Было взято с «Руководство к курсовой работе/Соболев В.И» (см.Список литературы №1)

Параллельный умножитель MPL. Обеспечить аппаратное умножение двойной и одинарной точности.

Требования к микропрограммному устройству управления:

§ AM29C331 (по выбору).

Емкость МПП килослов : 16

Функциональный состав и емкость основной памяти:

§ SRAM – 512кб, FlashFile – 32мб.

(разрядность – 32 бит)

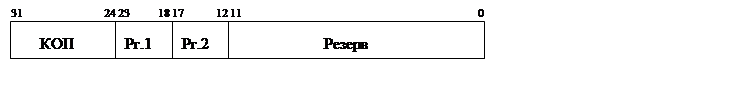

Команда состоит из одного или двух 32-х разрядных слов. Структура микроЭВМ обеспечивает выполнение следующих типов операций:

1) команда типа регистр-регистр:

КОП – код операции;

Рг.1 – приемник/источник данных;

Рг.2 – источник данных;

Оба операнда передаются напрямую на адресные входы А и В (см. структурную схему ОБ).

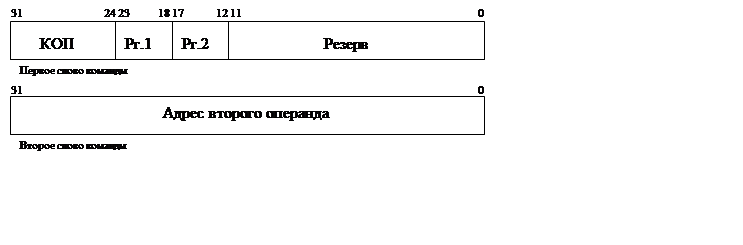

2) команда типа ОЗУ – регистр:

Рг.1 - приемник результата;

Рг.2 – регистр – источник 1-го операнда;

Команда предназначена для выполнения операции над данными из ячейки памяти и одного из регистров и помещения их в другой регистр.

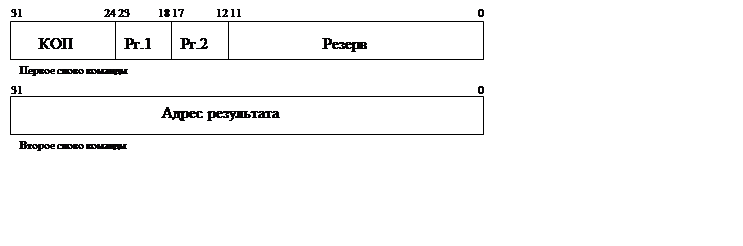

3) команда типа регистр – ОЗУ:

Рг.1 – источник первого операнда;

Рг.2 – источник второго операнда;

Команда предназначена для помещения в память результата операции над двумя регистрами.

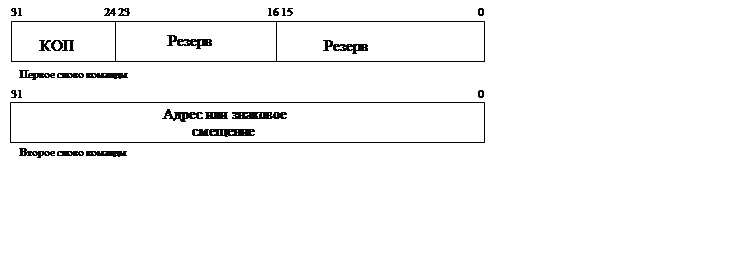

4) команда ветвления:

Команда предназначена для осуществления ветвления программы по условию задаваемому секвенсору. Знаковое смещение представляется в доп. коде и лежит в интервале от –2147483648 до 2147483647. Младший байт первого слова можно использовать для задания очень большого количества условий перехода.

Данные имеют формат 32 бит и хранятся в памяти в виде 32 разрядных слов, при считывании из памяти и записи в память действия производятся над 32-х разрядным словом.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.