МО и ПО РФ

НГТУ

Курсовая работа

по схемотехнике

Разработка прототипа ядра микроЭВМ.

Факультет: АВТ

Группа: АМ-810

Студент: Збоев А.Д.

Преподаватель: Соболев В.И.

Содержание

1. Цели и задание курсовой работы………………………..3

2. Форматы команд…………………………………………..4

3. Форматы поддерживаемых данных……………………...6

4. Особенности структуры ОБ………………………………6

5. Временные диаграммы ОБ………………………………...7

6. Формат статусного регистра………………………………8

7. Расчет минимальной длительности цикла ОБ……………9

8. Особенности структуры МУУ……………………………9

9. Расчет минимальной длительности цикла МУУ………...10

12.Формат микрокоманды……………………………………10

13. Расчет длительности цикла ядра микроЭВМ…………...12

14. Блок синхронизации……………….……………………..12

15. Схема начальной установки……………………………..12

18. Выводы к работе...………………………………………..13

19.Список используемой литературы ………………………14

1. Цели и задание курсовой работы

Целями данной курсовой работы являются:

· Освоение элементов методологии проектирования аппаратных средств вычислительной техники;

· Приобретение практического опыта разработки функциональных устройств и узлов, выполнения схемотехнических расчетов и оформления схемной документации;

· Закрепление и углубление знаний о современной элементной базе;

Задание к курсовой работе:

Разработать прототип ядра микроЭВМ, содержащий следующий набор устройств: микропрограммируемый микропроцессор (представлен как устройство, состоящее из микропрограммного устройства управления (МУУ) и операционного блока (ОБ)), основную память (ЗУ), средства интерфейса, обеспечивающие взаимодействие между процессором и ЗУ, блок синхронизации.

Прототип ядра микроЭВМ должен соответствовать следующим требованиям к его характеристикам и параметрам:

· Система команд гипотетическая. Форматы команд: одноадресные и безадресные;

· Количество программно доступных регистров общего назначения – не менее 8;

· Формат представления данных в процессоре – целочисленный в дополнительном коде и с разрядностью слова 16 бит;

· Минимальный доступный элемент данных памяти, непосредственно адресуемой процессором, - слово;

· Разрядность адреса памяти равна разрядности данных;

· Структура магистрали – трехшинная;

· Обмен данными процессор – память – синхронный без квитирования (без подтверждения готовности памяти и циклов ожидания процессора);

· Процессор должен быть оснащен схемными средствами поддержки начальной установки при включении, сбросе и возобновлении (после сбоев) питания.

· Процессорный модуль –Am29C116(аналог К1804ВМ1);

· Секвенсор микрокоманд – Am29C10, ёмкость МПП 4 Кслова;

· Основная память – SRAM 32 КВ, PROM 8 КВ;

· Принципиальная схема микропроцессора, блока синхронизации, схемы начальной установки.

Целью разработки ставятся наиболее существенные желаемые характеристики прототипа ядра микроЭВМ:

· высокое быстродействие (производительность);

· простота и надежность схемных решений.

Высокое быстродействие может быть достигнуто двумя путями - использованием высокоскоростных микросхем и разработкой такой архитектуры ядра гипотетической микроЭВМ, которая позволила бы сократить цикл прохождения микрокоманд через устройства ядра.

Под надежностью понимаются не количественные показатели, а отсутствие в схемах критических временных соотношений, рисков сбоя и гонок сигналов, использование унифицированных способов обмена между устройствами и т.п.

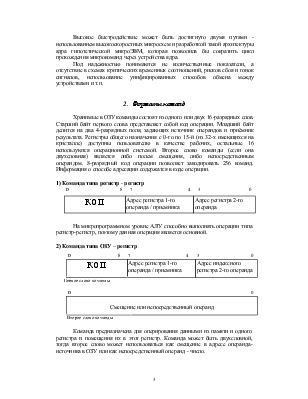

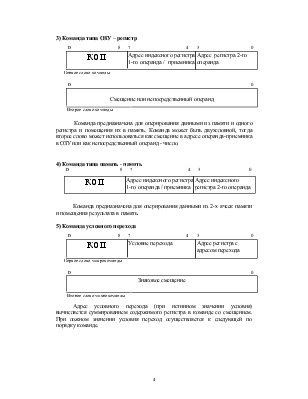

2. Форматы команд

Хранимые в ОЗУ команды состоят из одного или двух 16-разрядных слов. Старший байт первого слова представляет собой код операции. Младший байт делится на два 4-разрядных поля, задающих источник операндов и приёмник результата. Регистры общего назначения с 0-го по 15-й (из 32-х имеющихся на кристалле) доступны пользователю в качестве рабочих, остальные 16 используются операционной системой. Второе слово команды (если она двухсловная) является либо полем смещения, либо непосредственным операндом. 8-разрядный код операции позволяет закодировать 256 команд. Информация о способе адресации содержатся в коде операции.

|

|

|

|

|

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.