Рис. 3

|

14. Блок синхронизации

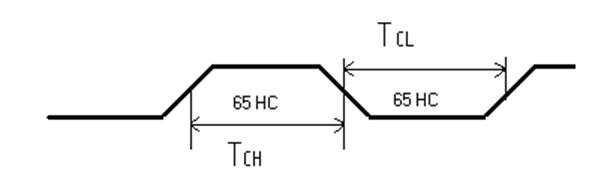

В качестве генератора, выдающего тактовый сигнал в схему, взята микросхема CY2071A фирмы Cypress – системный тактовый генератор, предназначенный для применения в составе блоков синхронизации центральных процессоров микроЭВМ и других вычислительных устройств в качестве задающего тактового генератора. Микросхема имеет стабилизированный с помощью внешнего кварцевого резонатора генератор опорной частоты от 10 до 25 МГц и может выдавать сигнал частотой от 500 кГц до 133 МГц (все параметры программируются заводом-изготовителем на заказ).

В качестве опорной частоты, определяемой кварцевым резонатором, выбрана частота 7.7 МГц (длительность такта примерно 130 нс.).

15. Схема начальной установки

Для сброса и первоначального запуска системы используется линия SYNRST, которая управляет мультиплексором на шине команд секвенсора. Пока эта линия установлена в «0», секвенсор выполняет команду JZ (переход по нулевому адресу). Для того, чтобы задержать ее в этом состоянии на некоторое время при включении питания, используется цепочка R1-C1. Пусть R1=1кОм и C1=510пФ, тогда обеспечиваемая задержка равна примерно 510 нс. Для получения более устойчивого сигнала асинхронный сброс снимается с RC-цепочки через два триггера Шмитта. Для преобразования асинхронного сброса в синхронный используется D-триггер: синхронный сброс повторяет асинхронный, но переключается не в любой момент времени, а только по фронту синхросигнала. В частности, при включении питания (и сбросе) на несколько тактов синхронный сброс находится в низком (активном) состоянии, после чего переходит в высокое (неактивное).

18. Выводы к работе

В результате проделанной работы было выполнено большинство требований, предъявляемых к разработке ядра микроЭВМ. Разрабатывая ядро микроЭВМ на основе блочно-иерархического принципа, удалось получить довольно целостную структуру.

В некоторых случаях настоящую схему можно было бы уменьшить, если бы мне удалось найти некоторые типы микросхемы. Например, можно было бы найти более быструю микросхему ПЗУ для построения ПНА – это уменьшило бы самый длинный в ядре микроЭВМ цикл.

Полезным оказалось бы в дальнейшем параллельное выполнение операций по генерации адреса и выполнение операций над данными. Это повысило бы быстродействие ядра микроЭВМ.

В процессе решения поставленной задачи был приобретен практический опыт разработки функциональных устройств и узлов, выполнения схемотехнических расчетов и оформления схемной документации, стало глубже понимание взаимосвязей между отдельными элементами схемы, были углублены мои знания современной элементной базы, были закреплены знания, полученные на теоретическом курсе схемотехники. В целом работа оказала большую помощь в приобретении практических знаний по разработке устройств ЭВМ.

19.Список используемой литературы и документации

1. Схемотехника. Руководство к курсовой работе. –Новосибирск: НГТУ, 1997.

2. Комплект БИС К1804 в процессорах и контроллерах / В.М. Мещеряков, И. Е. Лобов, С.С. Глебов и др.; Под ред. В.Б. Смолова – М.:Радио и связь, 1990-225 с.

3. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник в 2 томах./ Н.Н. Аверьянов, А.И. Березенко, Ю.И. Борщенко и др.; Под ред. В.А. Шахнова-М.: Радио и связь, 1988.- Т.1.- 368 с.- Т.2.- 386 с.

4. С. Т. Усатенко, Т. К. Каченок, М. В. Терехова. Выполнение электрических схем по ЕСКД. - М.: Издательство стандартов, 1992.

5. И.И.Петровский, А.В.Прибыльский, В.С.Чувелев. Логические ИС КР1553, КР 1554. Справочник.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.