Параллельный умножитель имеет два 16-разрядных входных и один 16-разрядный выходной порты данных. Выполняет знаковое и беззнаковое умножение целых чисел однократной и двойной точности. Внутренние регистры с общей синхронизацией и индивидуальным управлением записью.

Входы ENA#, ENB# соединены через инвертор и управляются одним битом, который разрешает загрузку операндов для умножения во внутренние регистры умножителя. Входы OEM# и OEL# также объединены через инвертор и управляются одним битом.

Входы RND, ENR соединены, это позволяет получить результат операции умножения однократной и двойной точности.

При активизировании данного входа:

- подача сигнала высокого уровня, включается режим округления произведения до 16 разрядов, а так же режим прозрачности, который дает возможность сквозного прохождения результата операции произведения помимо регистров результата (младшей и старшей части) на выходную шину данных умножителя. Это позволяет уменьшить количество циклов для получения полного конечного результата операции умножения.

- при подаче низкого уровня, включается режим умножения чисел для получения результата двойной точности. Формат результата операции умножения будет 32 разрядным, который хранится в регистрах результата (регистры младшей и старшей части произведения).

На входы RS и FT подано напряжение питания Ucc равное 3,7В.

Регистры операционного блока - регистры входных и выходных данных, приемопередатчик. Так как регистры серии КР1554ИР23 записывают (и хранят эти данные) по каждому положительному фронту синхросигнала, то для обеспечения передачи и приема необходимых данных, на вход OE# разрешения выводов подается микрокоманда.

В качестве мультиплексоров выбора адресов РОН используются мультиплексоры отечественного производства КР1554КП16. Управление мультиплексором берется из микрокоманды.

5.Временные диаграммы ОБ

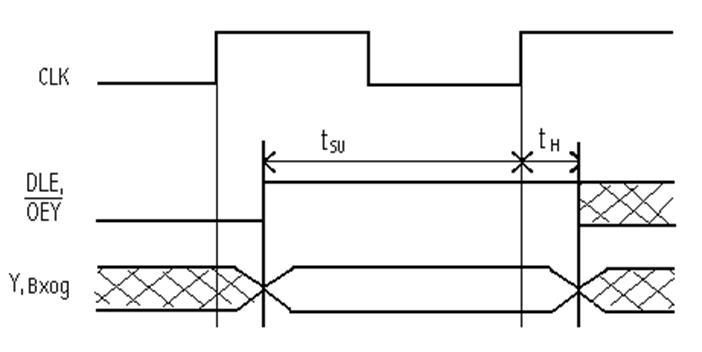

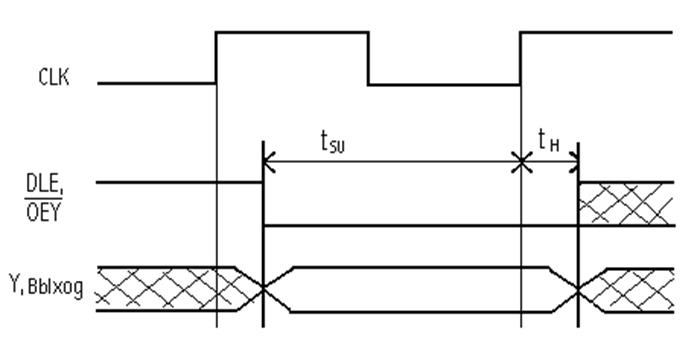

Временные диаграммы управления портом Y ЦПЭ приведены на рисунке 1 – вод данных и 2 – вывод данных.

Рис. 1

|

Рис. 2

|

6. Формат статусного регистра

Статусный регистр является встроенным в ЦПЭ К1804ВМ1.

В младшие 4 разряда SRG могут быть записаны состояния АЛУ: нуль(Z), перенос (С), знак (N), переполнение (OVR) или 4 младших бита данных с шины Y в зависимости от выполняемой инструкции. Запись в младшие 4 разряда SRG производится после выполнения всех инструкций, за исключением следующих: “нет операции”, “хранение содержимого SRG”, “проверка состояния”, “установка в 1” и “установка в 0” старших битов SRG. В старших четырех разрядах SRG хранятся бит связи (L) и три флага (FL1,FL2,FL3), определяемые пользователем. Запись в старшие разряды SRG производится с шины Y после выполнения инструкций “установка в 1” или “установка в 0” старших битов SRG, а также “загрузка SRG ”. Запись бита связи (L) производится также после каждой инструкции сдвига.

Формат статусного регистра наглядно представлен таблицей 1.

Табл. 1

|

0 |

Z |

Флаг нуля |

|

1 |

C |

Флаг переноса |

|

2 |

N |

Флаг знака |

|

3 |

OVR |

Флаг переполнения |

|

4 |

L |

Флаг бита связи |

|

5 |

FL1 |

Пользовательский флаг №1 |

|

6 |

FL2 |

Пользовательский флаг №2 |

|

7 |

FL3 |

Пользовательский флаг №3 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.