МИНИСТЕРСТВО ОБЩЕГО И ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

НОВОСИБИРСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

КАФЕДРА ВТ

Расчётно-графическая работа

по дисциплине «Схемотехника»

«Разработка памяти»

Факультет: АВТ

Группа: АМ-309

Студент: Трофимов А.В.

Преподаватель: Соболев В.И.

НОВОСИБИРСК 2005

Оглавление.

Введение.

Разработка памяти включает в себя несколько этапов: получение технического задания; выбор типономиналов микросхем памяти, отвечающих требованиям, предъявленным в техническом задании; выбор типономиналов микросхем, выполняющих функции интерфейсных элементов (они также должны удовлетворять требованиям технического задания); расчёт нагрузки (токовой, ёмкостной), создаваемой микросхемами памяти на линии адреса, данных, управления; расчёт временных параметров разработанной памяти (время доступа, время цикла); расчёт энергопотребления (в случае необходимости, если оно лимитировано в техническом задании). В том случае, если какие-либо рассчитанные параметры (нагрузочные, временные) не отвечают требованиям, предъявленным в техническом задании, то либо принимается решение о выборе других типономиналов микросхем памяти (интерфейсных элементов), либо данная ситуация оговаривается разработчиком (например, насколько существенно отклонение параметра от нормы и как это может повлиять на работу памяти вцелом).

При разработке также необходимо учитывать особенности конкретных типов памяти (например, для перепрограммируемой памяти нужно описать режимы программирования и стирания).

Цель работы: разработать память, удовлетворяющую требованиям технического задания. Наиболее важным является обеспечение времени доступа к памяти в пределах заданной нормы. Нежелательно также, чтобы фактическое время доступа было намного меньше указанного в техническом задании.

1. Техническое задание.

Разработать память, состоящую из статической оперативной памяти (SRAM) и флэш-памяти с файловой организацией (Flash File). Информационная ёмкость для памяти SRAM – 8МБ, для Flash-памяти – 8МБ. Разрядность слова для обоих типов памяти – 32 бит. Время цикла – не более 150 нс. Системная магистраль для взаимодействия с памятью – с трёхшинной структурой (шина адреса, шина данных, шина управления). Электрический интерфейс – ТТЛ.

2. Выбор элементной базы.

При заданных информационной ёмкости и разрядности (8МБ, 32бит) получаем информационную организацию для каждого типа памяти – (2Мх32)бит. Выбираемые микросхемы памяти должны максимально подходить по информационной организации, а также отвечать другим требованиям технического задания. Кроме того, микросхемы Flash-памяти и памяти SRAM должны иметь одинаковое напряжение питания (чтобы использовать один источник). С учётом этих требований были выбраны следующие типономиналы микросхем:

Для памяти типа SRAM – CY7C1071AV33-12 [1]. Её характеристики:

· Информационная организация – (2Мх16)бит.

· Максимальное время доступа – 12 нс.

· Напряжение питания – 3.3±0.3В.

· ТТЛ-совместимые входы и выходы.

Для памяти типа Flash – S29GL032M [2]. Её характеристики:

· Информационная организация – (2Мх16)бит.

· Максимальное время доступа – 90 нс.

· Напряжение питания – 3.3±0.3В.

Техническая документация и описание выбранных микросхем приведены в приложении.

3. Разработка структурной схемы.

Согласно техническому заданию, оба типа памяти (SRAM и Flash) должны иметь одинаковую информационную организацию (2Мх32). По входам адреса, входам/выходам данных и входу WE# они соединяются параллельно. Сигналы с шины адреса, как и сигнал WE#, необходимо буферизировать. Поэтому эти сигналы поступают на микросхемы памяти через буфер. Связь с шиной данных осуществляется посредством трансивера. Сигналы CE (для SRAM) и CE# (для Flash) формирует адресный селектор, который анализирует сигнал MEMR (обращение к памяти), поступающий с шины управления и некоторые биты шины адреса (для правильного обращения к нужному типу памяти). Чтобы знать, какие именно биты нужно проанализировать в адресном селекторе, необходимо разработать карту памяти.

Карта памяти.

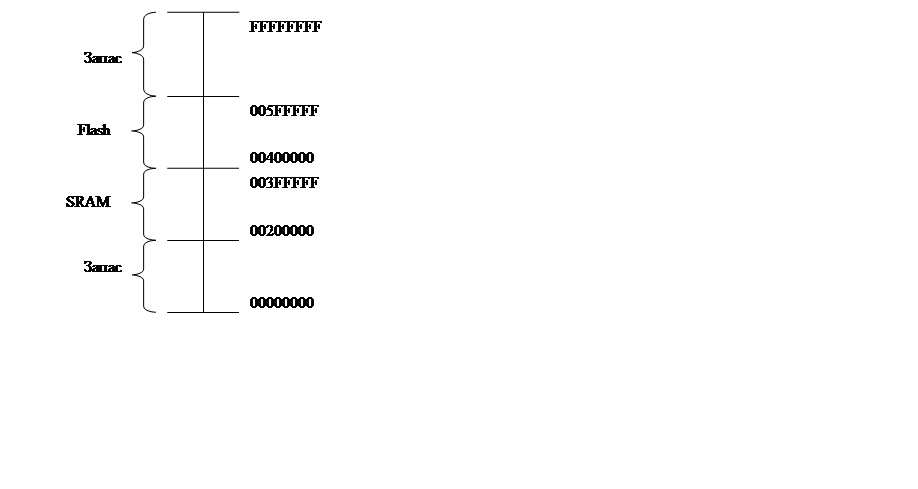

Разрядность шины адреса в нашем случае равна 32. Ёмкость микросхем памяти обоих типов составляет 2М слов. 2Мбит=221бит. Следовательно, для адресации обоих типов памяти требуется 21 бит адреса (А20…А0). Кроме того, каждому типу памяти должно быть выделено своё адресное пространство. Для этого назначим 22-й бит (А21) для выбора памяти SRAM, 23-й бит (А22) для выбора памяти Flash. Остальное адресное пространство будем считать резервным, т.е. оно может быть использовано для адресации других внешних по отношению к нашей памяти устройств (например, другой памяти). С учётом сказанного нарисуем карту памяти (рис.1).

Рис.1. Карта памяти.

С учётом вышесказанного, а также построенной карты памяти, строим структурную схему памяти (рис.2).

AB – системная шина адреса;

DB – системная шина данных;

CB – системная шина управления;

BF – буфер;

TR – трансивер;

ADDRSEL – адресный селектор;

MEMR – сигнал обращения (запроса) к памяти;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.